August 2013 Master's Degree Thesis

# Online Fault Detection and Reconfiguration of ALU using Scalable Error Detection Coding Scheme

# Graduate School of Chosun University

Department of Computer Engineering

Zahid Ali

# 확장가능한 에러탐지코딩기법 활용 실시간 오류탐지 및 재구성이 가능한 연산기

Online Fault Detection and Reconfiguration of ALU using Scalable Error Detection Coding Scheme

August 23, 2013

Graduate School of Chosun University

Department of Computer Engineering

Zahid Ali

# Online Fault Detection and Reconfiguration of ALU using Scalable Error Detection Coding Scheme

Advisor: Prof. Jeong-A Lee

This Thesis is submitted to Graduate School of Chosun University in partial fulfillment of the requirements for a Master's degree

April 2013

Graduate School of Chosun University

Department of Computer Engineering

Zahid Ali

### Thesis Examination Committee

#### 2013 년 4 월

# Graduate School of Chosun University

I dedicate this thesis to my parents, Roshan Ali & Rahat Tameez for their love and support, and to my teachers, especially Dr. Shoaib Zaidi for his trust in me.

# **Table of Contents**

| Tal                   | ole of Contents                                                                                                                                                                                                                                                                                  | v                                       |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|                       | t of Figures                                                                                                                                                                                                                                                                                     |                                         |

|                       | t of Tables                                                                                                                                                                                                                                                                                      |                                         |

|                       | t of Acronyms                                                                                                                                                                                                                                                                                    |                                         |

| 초                     | 록                                                                                                                                                                                                                                                                                                | 11                                      |

|                       |                                                                                                                                                                                                                                                                                                  |                                         |

| I.                    | Introduction                                                                                                                                                                                                                                                                                     |                                         |

| A.                    | Research Motivation                                                                                                                                                                                                                                                                              |                                         |

| B.                    | Research Objectives                                                                                                                                                                                                                                                                              |                                         |

| C.<br>D.              | Thesis Contributions<br>Thesis Organization                                                                                                                                                                                                                                                      |                                         |

| D.                    |                                                                                                                                                                                                                                                                                                  |                                         |

| II.                   | Overview and Related Work                                                                                                                                                                                                                                                                        | 16                                      |

|                       | Scalable Error Detection Coding Scheme                                                                                                                                                                                                                                                           | 10                                      |

|                       | Scalable Lifter Detection County Scheme                                                                                                                                                                                                                                                          |                                         |

| A.                    | SEDC <sub>2</sub> Code                                                                                                                                                                                                                                                                           |                                         |

| B.                    | SEDC <sub>3</sub> Code                                                                                                                                                                                                                                                                           |                                         |

| C.                    | SEDC <sub>4</sub> Code                                                                                                                                                                                                                                                                           |                                         |

| IV.                   | Introduction to Overall System                                                                                                                                                                                                                                                                   | 23                                      |

| A.                    | ALU                                                                                                                                                                                                                                                                                              |                                         |

| B.                    | SEDC encoded ALU                                                                                                                                                                                                                                                                                 |                                         |

| C.                    | TSC SEDC checker                                                                                                                                                                                                                                                                                 |                                         |

| v                     |                                                                                                                                                                                                                                                                                                  |                                         |

| ۷.                    | Formulation of SEDC encoded ALU                                                                                                                                                                                                                                                                  | 25                                      |

|                       |                                                                                                                                                                                                                                                                                                  |                                         |

| <b>ч.</b><br>А.<br>В. | 2-, 3- and 4-bit SEDC encoded Boolean Operation Unit                                                                                                                                                                                                                                             | 25                                      |

| A.                    |                                                                                                                                                                                                                                                                                                  | 25                                      |

| A.<br>B.              | <ul><li>2-, 3- and 4-bit SEDC encoded Boolean Operation Unit</li><li>2-, 3- and 4-bit SEDC encoded Shift/Rotate Unit</li></ul>                                                                                                                                                                   |                                         |

| A.<br>B.<br>C.<br>D.  | <ul> <li>2-, 3- and 4-bit SEDC encoded Boolean Operation Unit</li> <li>2-, 3- and 4-bit SEDC encoded Shift/Rotate Unit</li> <li>2-, 3- and 4-bit SEDC encoded Add/Subtract Unit</li> </ul>                                                                                                       |                                         |

| A.<br>B.<br>C.<br>D.  | <ul> <li>2-, 3- and 4-bit SEDC encoded Boolean Operation Unit</li> <li>2-, 3- and 4-bit SEDC encoded Shift/Rotate Unit</li> <li>2-, 3- and 4-bit SEDC encoded Add/Subtract Unit</li> <li>2-, 3- and 4-bit SEDC encoded Compare Unit</li> </ul>                                                   | 25<br>                                  |

| A.<br>B.<br>C.<br>D.  | <ul> <li>2-, 3- and 4-bit SEDC encoded Boolean Operation Unit</li> <li>2-, 3- and 4-bit SEDC encoded Shift/Rotate Unit</li> <li>2-, 3- and 4-bit SEDC encoded Add/Subtract Unit</li> <li>2-, 3- and 4-bit SEDC encoded Compare Unit</li> <li>Scaling SEDC encoded ALU for n-bit Input</li> </ul> | 25<br>26<br>27<br>29<br><b>30</b><br>30 |

| D.   | n-bit SEDC encoded Compare Unit                             |    |

|------|-------------------------------------------------------------|----|

| VII. | TSC SEDC checker                                            | 33 |

| A.   | Difference between SEDC and Berger code checker             | 33 |

| В.   | Logic and circuits for TSC SEDC checkers                    |    |

| 1.   | TSC SEDC1 checker                                           |    |

| 2.   | $TSC \ SEDC_2 \ checker$                                    |    |

| 3.   | $TSC SEDC_3$ checker                                        |    |

| 4.   | $TSC SEDC_4$ checker                                        |    |

| 5.   | $TSC \ SEDC_n$ checker                                      |    |

| VIII | . Fault coverage of SEDC encoded ALU                        | 38 |

| A.   | Fault Model                                                 |    |

| 1.   | Type 1 error                                                |    |

| 2.   | Type 2 error                                                |    |

| 3.   | Type 3 error                                                |    |

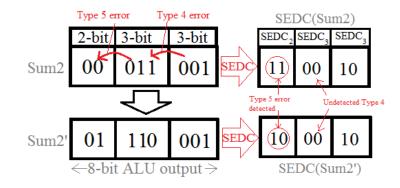

| 4.   | Type 4 error                                                |    |

| 5.   | Type 5 error                                                |    |

| B.   | Fault Secureness                                            | 40 |

| 1.   | Against Type 1 error                                        | 40 |

| 2.   | Against Type 2 error                                        | 40 |

| 3.   | Against Type 3 error                                        | 40 |

| 4.   | Against Type 4 error                                        | 41 |

| 5.   | Against Type 5 error                                        | 41 |

| C.   | Overall Fault Coverage                                      | 42 |

| IX.  | Results of Fault testing on TSC SEDC checker                | 43 |

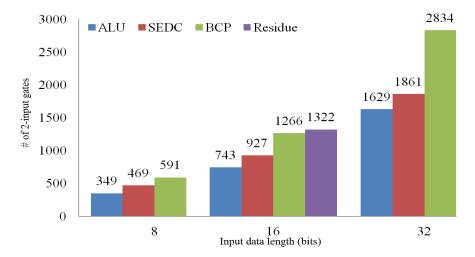

| X. ( | Comparison of Area, Delay, Complexity and Power dissipation | 45 |

| A.   | SEDC encoded ALU                                            | 45 |

| 1.   | Area Overhead                                               | 45 |

| 2.   | Delay                                                       |    |

| 3.       | Complexity in Scaling and Power dissipation                                          |

|----------|--------------------------------------------------------------------------------------|

| B.       | TSC SEDC checker                                                                     |

| 1.<br>2. | Area Overhead                                                                        |

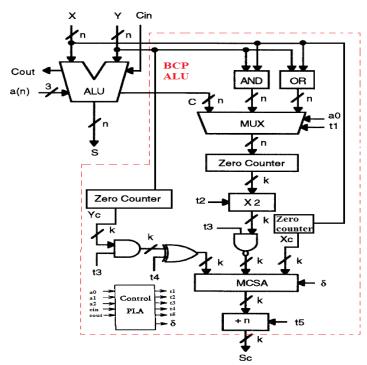

|          | Prototyping the SEDC based error detecting and reconfiguring ALU hitecture on FPGA51 |

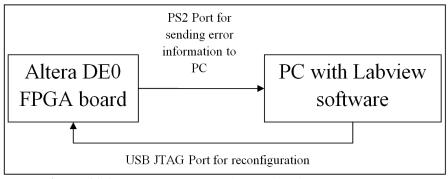

| A.       | Overall FPGA based system design                                                     |

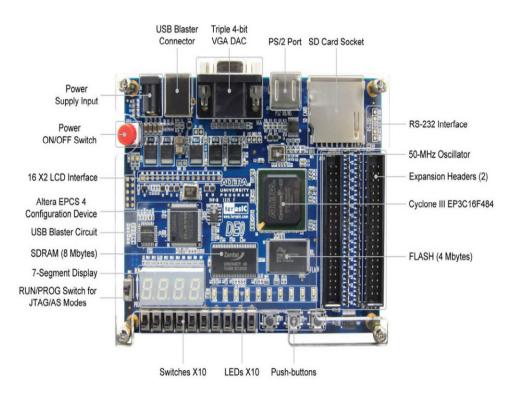

| 1.<br>2. | Altera DE0 FPGA board                                                                |

| B.       | Implementation Results and Area Comparison54                                         |

| XII.     | Conclusion and Future Considerations56                                               |

| Bib      | liography58                                                                          |

| AB       | STRACT (English)61                                                                   |

| AC       | KNOWLEDGMENT63                                                                       |

# List of Figures

| Fig. 3.1: Data partitioning and encoding using SEDC scheme for given data word      |

|-------------------------------------------------------------------------------------|

| Fig. 3.2: 2D illustration of SEDC <sub>2</sub> scheme                               |

| Fig. 3.3: 3D illustration of SEDC <sub>3</sub> scheme and SEDC <sub>3</sub> circuit |

| Fig. 4.1: General model for SEDC based Self-checking ALU.                           |

| Fig. 7.1: Archietectures of TSC (a) Berger checker (b) SEDC checker                 |

| Fig. 7.2: MOS level implementation of TSC SEDC <sub>1</sub> checker                 |

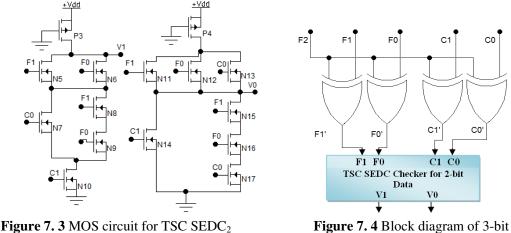

| Fig. 7.3: MOS level implementation of TSC SEDC <sub>2</sub> checker                 |

| Fig. 7.4: Block diagram of TSC SEDC <sub>3</sub> checker                            |

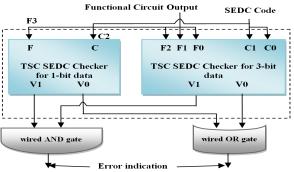

| Fig. 7.5: Block diagram of TSC SEDC <sub>4</sub> checker                            |

| Fig. 7.6: Block diagram of TSC SEDC <sub>n</sub> checker                            |

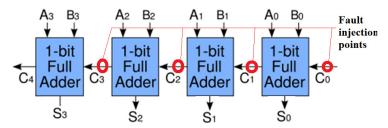

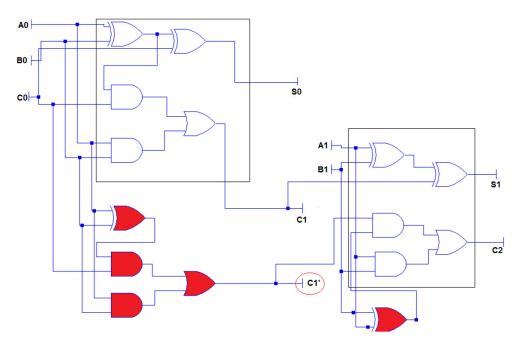

| Fig. 8.1: Fault injection points in a ripple carry adder                            |

| Fig. 8.2: Adding redundant carry generating circuit to cope with Type 3-B errors    |

| Fig. 8.3: ALU organization that eliminates multiple random errors                   |

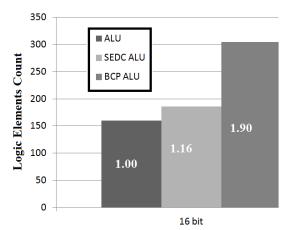

| Fig. 10.1: Area utilization chart for SEDC encoded, BCP and simple ALU              |

| Fig. 10.2 : Berger Check Prediction Arithmetic and Logic Unit.                      |

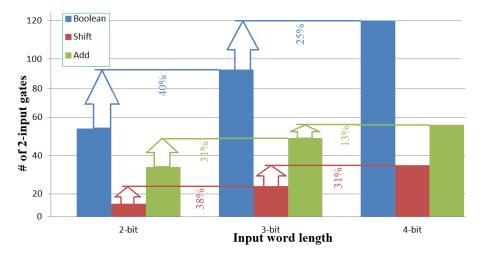

| Fig. 10.3: Increasing trend in SEDC encoded ALU hardware                            |

| Fig. 11.1: Overall prototype diagram for fault tolerant ALU                         |

| Fig. 11.2: DE0 Board                                                                |

| Fig. 11.3: Area comparison of FPGA implementation of 16-bit normal ALU, SEDC        |

| ALU and BCP ALU.                                                                    |

### List of Tables

| Table 5-1: Logic for 2-bit SEDC encoded BO unit                         |

|-------------------------------------------------------------------------|

| Table 5-2: Logic for 2-bit SEDC encoded SRO unit                        |

| Table 5-3: Logic equations for S1, sibit, S14-S15 signals               |

| Table 5-4: Logic for 2-bit SEDC encoded Compare Unit                    |

| Table 6-1: Logic for scaling n-bit SEDC encoded SRO unit                |

| Table 6-2: Logic for scaling n-bit SEDC encoded ASO unit                |

| Table 7-1: '10' codes table for one bit input(SEDC <sub>1</sub> )       |

| Table 9-1: Results of single faults on TSC SEDC <sub>1</sub> checker    |

| Table 10-1: Area comparison between SEDC and Berger checker             |

| Table 10-2: Critical Path (C.P) delay comparison of TSC Berger and SEDC |

| checker                                                                 |

| Table 11-1 : Function of selection switches and seven segments          |

# List of Acronyms

| ASO               | Add/Subtract Operation             |

|-------------------|------------------------------------|

| TSC               | Totally Self Checking              |

| CDF               | Chain Description File             |

| ALU               | Arithmetic and Logic Unit          |

| BCP               | Berger Check Prediction            |

| BCH               | Bose Chaudhuri Hocquenghem         |

| CO                | Compare Operation                  |

| SEDC              | Scalable Error Detection Coding    |

| SEDC <sub>2</sub> | SEDC codes for 2-bit input         |

| SEDC <sub>3</sub> | SEDC codes for 3-bit input         |

| SEDC <sub>4</sub> | SEDC codes for 4-bit input         |

| SFS               | Strongly Fault Secure              |

| AUED              | All Unidirectional Error Detection |

| MOS               | Metal Oxide Semiconductor          |

| CED               | Concurrent Error Detection         |

| BO                | Boolean Operation                  |

| SRO               | Shift/Rotate Operation             |

| DMR               | Double Modular Redundancy          |

| FPGA              | Field Programmable Gate Array      |

| FF                | Flip Flop                          |

| LSB               | Least Significant Bit              |

| MSB               | Most Significant Bit               |

| SEU               | Single Event Upset                 |

| VLSI              | Very Large Scale Integration       |

| SRAM              | Static Random Access Memory        |

| TMR               | Triple Modular Redundancy          |

|                   | 1                                  |

#### 초 록

# 확장가능한 에러탐지코딩기법 활용 실시간 오류탐지 및 재구성이 가능한 연산기

#### 시디키 샤이크 자히드 알리 지도교수: 이정아, 교수, Ph.D. 컴퓨터공학과 조선대학교 대학원

마이크로 전자 회로 및 SRAM 기반의 FPGA 디바이스는 트랜지스터의 크기 감소 및 높은 패키징 밀도로 인한 고장 및 오류에 더 취약해지고 있기 때문에, 오류 검출은 시스템 신뢰성 측면에서 아주 중요한 문제이다.

오류는 크게 소프트 오류와 하드 오류로 분류할 수 있다. 하드 오류는 지속적인 결함으로 발생하나, 소프트 오류는 일시적 또는 간헐적으로 결함이 발생한다. 지금까지 알려진 바에 의하면, 오류의 대부분이 일시적인 오류로 인해 발생된다.

일시적인 오류로 인한 소프트 오류를 검출하는 기술은 일반적으로 프로세서의 성능감소를 가져오거나, 오류 검출에 필요한 추가적인 하드웨어 자원 및 전력소모가 요구되어 이의 적절한 조율과정을 거치게 된다. 이중 모듈 방식은 공통 모드 고장 (CMF)을 포함하여 대부분의 오류에 대응할 수 있지만, 구현상의 변화를 주어야 하고, 하드웨어 자원측면에서 두 배의 오버 헤드 비용이 필요하다. 삼중 모듈 방식(TMR)은 구현상의 변화없이 같은 모듈을 세 번 반복하여 사용할 수는 있으나, 하드웨어 오버헤드 비용이 높고, 각 모듈의 동일한 출력을 비교하기 위해 voting 회로가 필요하다. 추가적인 하드웨어 오버헤드를 피하기위하여, 피연산자를 회전 또는 이동하여 연산을 다시 한 후, 오류를 검출하기도 하는데, 이 경우 연산에 소요되는 시간이 추가되어 이 또한 시스템의 시간적인 오버헤드가 된다. 연산 중 오류검출 (CED) 방법은 산술 코드, 버저 코드, 패리티 코드 등을 사용하여 인코딩을 한 상태에서 연산을 수행한다. CED 기술의 효율적인 구현을 위해, 발생할 가능성이 높은 결함유형을 고려하는 것이 중요하다. VLSI 회로에서 고장은 일반적으로 단일방향 오류인 것으로 알려졌다. 단일방향 오류는 동시에 0 에서 1 또는 1 에서 0 으로 오류가 발생되지 않으며, 오류의 방향이 단일방향인 오류이다. 단일방향 오류 감지 (AUED) 기술은 하드웨어 자원 오버 헤드를 고려할 때, 오류 감지의 효율을 높인다. 본 논문에서는 여러개의 단일방향 오류를 탐지할 수 있는 확장 가능한 오류탐지 코딩 (SEDC)을 활용한다. SEDC 방식은 입력 데이터를 4-비트 이하로 분할하고, 분할 된 데이터를 동시에 인코딩하여 오류탐지코드를 할당한다. 따라서, 기존의 단일방향 오류탐지 방식과 달리, 입력데이터의 크기 'n'이 증가하더라도, 오류탐지코드 생성에 소요되는 시간은 증가되지 않으며, 기본 모듈들의 활용이 가능하여 구현의 복잡성도 증가되지 않는다.

본 논문에서는 SEDC 방식을 사용하여, 단일 이벤트 오류발생에 대해 높은 내결함성을 가진 ALU 구조를 제안한다. 기존 관련연구에 비하여 제안된 SEDC 코드 기반 ALU는 하드웨어 오버헤드와 지연시간 측면에서 더 나은 결과를 보인다. SEDC 기반 32 비트 ALU의 ASIC 구현은 버저 코드 예측 ALU에 비하여 하드웨어 자원을 34% 절약했다 [5]. SEDC 기반 16 비트 ALU의 FPGA 구현은 버저 코드 예측 ALU에 비하여 하드웨어 자원을 39% 감소시켰다. 이와 더불어, SEDC 기반 확장가능한 자가완전검증회로(TSC)가 하드웨어 자원과 지연시간을 고려할 때 매우 효율적임을 보였다. 32 비트인 경우, 버저코드 기반 TSC 에 비하여 SEDC 기반 TSC을 사용하였을 때, 하드웨어 자원 사용량이 67% 감소하였고, 지연시간은 81% 향상되었음을 보였다. 추가적으로, 하드 오류를 완화하기 위해 FPGA 의 재구성 기능을 활용할 수 있음도 보였다.

#### I. Introduction

#### A. Research Motivation

System reliability has become a major concern as the transistor size decreases [1]. The consequence of increasing complexity in the functionality of applications accelerated the demand of more reliable system. On the other hand, people don't want to return back to less sophisticated systems due to the grown dependence on luxuries automated systems.

Initially, reliable computing was limited to military, industrial, aerospace, and communications applications in which the outcome of computer failure had major economic impact or even loss of life. Nowadays, even commercial and day to day life applications require high reliability as we move towards the era of wired money transfer and automated life-style. Reliability is of vital importance in situations where a computer failure could have disastrous results [2].

Errors can be classified as either soft errors or hard errors. Soft errors are caused by transient or intermittent faults, while hard errors are caused by permanent faults. Permanent faults remain for indefinite periods until corrective action is taken. Studies show that the majority of errors are caused by transient faults.

Studies shows that most of the errors originate from Arithmetic logic unit (ALU) of a microprocessor based system [3], which is used in almost every automation application. From space applications to a simple money transfer, error could cause disaster. For example, a permanent fault in ALU calculation for navigational data may result in the lost of a ten billion dollar shuttle in space for ever. During a money transfer, a single flip of bit in the transferring amount can cause huge deficit to an individual.

Hence a fault tolerant ALU has become the most important part of such applications.

#### **B.** Research Objectives

Many error detection techniques have been proposed so far. Usually, a tradeoff is made between the performance of a processor and the area and power required for error detection. For efficient implementation of CED techniques, it is important to consider the relevant types of faults that are supposed to be more probable to occur. The types of faults within a VLSI circuit have been analyzed and found to be of the type which would tend to affect the bits in a unidirectional manner [4]. Unidirectional errors can alter the node logic from zero to one or from one to zero, but not both at the same time. So an All Unidirectional Error Detection (AUED) technique provides optimal fault coverage with reduced area overhead.

Our main objective is to reduce the area penalty with 100% fault coverage against unidirectional errors. Delay between occurrence and detection of fault can also play a vital role. If a fault is detected after it is being propagated, then the overall system might fail, hence delay is also one of the key objectives of our research. We will also take in to account the power distribution so as to avoid the hot spots in the design. Lastly, our focus will be on reducing the complexity of overall system when scaling the circuits for higher input data lengths.

#### C. Thesis Contributions

The main aim of this research is to come up with a fault tolerant ALU using newly developed AUED technique named Scalable Error Detecting (SEDC) scheme with a better hardware and delay overhead as compared to the previous CED techniques. In order to achieve this, we will formulate and design the SEDC encoded ALU for predicting the SEDC code word of a particular ALU output word. As the name employs, SEDC is scalable with respect to input data length, while the latency of the circuit remains constant. SEDC splits the input data into smaller segments (2-, 3- and 4-bits) and encodes them in parallel (using SEDC<sub>2</sub>, SEDC<sub>3</sub> and SEDC<sub>4</sub> coding schemes respectively). This inherited parallelism makes our scheme faster. Moreover, the scaling requires few modifications in the basic circuit resulting in less complex structure.

SEDC scheme uses four basic coding schemes, namely  $SEDC_2$ ,  $SEDC_3$  and  $SEDC_4$ . For bigger input data length, multiple copies of these basic coding schemes are used. Hence, the power distribution of overall circuit is very uniform.

We will also present the design and implementation of Totally Self-checking (TSC) checker for SEDC scheme. This checker also exploits the parallelism concept like the code

generating part, hence the SEDC checker also exhibit constant latency, no matter how long the input data length is.

The prototype of a complete 8-bit error detecting and reconfigurable ALU system will also be illustrated on FPGA.

Result shows that SEDC based ALU outperforms other coding schemes in terms of delay, while it takes less area than Berger Code Prediction ALU [5] which is known to be the only coding scheme used for implementing fault secure ALU [6].

#### **D.** Thesis Organization

The rest of this thesis is organized as follows: the overview of previous work related to this topic has been presented in chapter II. Theoretical background of SEDC scheme is given in chapter III and the overall block diagram of SEDC based self-checking ALU is discussed in chapter IV. With the help of logic equations, first the method of encoding 2-, 3- and 4-bit Boolean Logic, Shift/Rotate and Add/Subtract operation units using SEDC scheme is illustrated in chapter V and then, the scaling of ALU for any input bit length 'n' is elaborated in chapter VI. The design details of TSC SEDC checker is covered in chapter VII. We will discuss the fault coverage of SEDC based self-checking ALU and the TSC SEDC checker in chapter VIII & IX respectively. Chapter X is dedicated for comparing the area, delay and complexity of SEDC scheme with existing self-checking ALU techniques. The FPGA implementation of SEDC based error detecting ALU is discussed and evaluated in Chapter XI. Finally, the conclusion with future goals are discussed in last chapter.

#### **II.** Overview and Related Work

Self-checking ALU provides concurrent error detection (CED) capability that can be used to design a fault tolerant computer system. A duplex structure (or double modular redundancy, i.e., DMR) provides high fault security but require twice the area overhead as compared to the area of a simple ALU. Checker in DMR system accommodate exactly twice the number of check bits which increases the area overhead of the checker as well. For example, if a 64-bit fault tolerant ALU is implemented using DMR technique then the checker for DMR system must encompass 128-bit (or more). For system to be TSC, the checker must be TSC as well. A 128-bit TSC checker must contain tree structure of two rail checkers that not only increases the overall area of the system, but also the delay as well. Hence, systems with larger inputs are proposed not to be protected by DMR technique [7].

Fault tolerance by shifted and rotated operands in TMR [8] is proposed for high fault security, but the technique requires three copies of same ALU. Moreover, the shifting and rotating operations slow down the whole process, and hence limits the overall speed of the microprocessor. The outputs of the three ALU modules have to be checked using a voter circuitry, which produces erroneous outputs when two copies of any module in the system fail. The voter circuitry has to cover 3 times the numbers of outputs than the outputs of a single ALU. For a 128-bit TMR ALU, the voter circuit has to accommodate 384-bit inputs which tremendously increases the overall area overhead of the system.

In [9], hardware and time redundancy are combined to achieve fault detection, diagnosis as well as isolation of the faulty module with 75% more area overhead than a normal ALU. The technique is based on the fact that a 32-bit ALU can be implemented using two 16-bit ALUs. If one of the ALU struck by a permanent fault, the other 16-bit ALU can compute the 32-bit result with some degradation in system performance. For the system to work as TSC, the system must employ TSC multiplexers (i.e., differential multiplexers) for multiplexing the outputs and inputs of the smaller ALUs, which adds to area overhead. The control unit must also exhibit self-testing properties, otherwise it will become the single point of failure to the system.

For efficient implementation of CED techniques, it is important to consider the relevant types of faults that are more likely to occur. The types of faults within a VLSI circuit have been analyzed and found to be of the type which would tend to affect the bits in an unidirectional manner [10]. Unidirectional errors can alter the node logic from zero to one or from one to zero, but not both at the same time [4],[10],[11]. All Unidirectional Error Detection (AUED) techniques provide optimal fault coverage with reduced area overhead as compared to simple duplication (DMR) or triplication (TMR).

Several error detection schemes have been proposed to detect unidirectional errors in computer hardware. Berger Code scheme is the most popular AUED scheme. In [5], Berger Check Prediction (BCP) circuit is proposed for detecting unidirectional errors in the ALU circuit. The BCP circuit generates the check symbol for the n-bit ALU result using the zero's counts of the operands as well as the internally generated carries. Although the use of internally generated carries for computation of check bits makes the scheme strongly fault secure (SFS), but this also increases the latency of the overall system. Latency of Berger code checker also adds into this delay. Results in [12] show that FPGA implementation of BCP ALU requires 45% more area overhead than the area occupied by normal ALU.

Arithmetic codes like Residual codes are efficient for checking arithmetic units because these codes reside under most arithmetic operations [13]. Arithmetic codes can ensure fault secureness for most arithmetic operators [14], but arithmetic code checking has some drawbacks. Logic and shift operations do not preserve arithmetic codes. Therefore, using such codes in ALU and shifter requires the implementation of complex circuitry. Also, arithmetic codes don't provide 100% fault coverage against all unidirectional errors. An efficient fault tolerant ALU using residual codes [15] for whole data path is proposed, but if only ALU is considered then this technique occupies the same area as DMR. The circuit also uses internal carry vectors for CED which makes it slower than the DMR technique.

For applications where only t-unidirectional errors are required to be detected, [16] proposes a modification of BCP ALU using Bose-Lin codes, with less area overhead than [5]. Similar to BCP circuitry, the Bose-Lin Check Prediction circuitry also uses input operands

and internally generated carries from normal ALU to generate the check symbols. Hence, the worst case time response of [5] and [16] is almost the same.

No scaling scheme is given in [5] while Bose-Lin based Check Prediction circuitry is not easily scalable. As the check bits increase above three bits, the arithmetic circuits require complete change in some parts of the circuitry.

In [17] error correcting codes are proposed for designing 32-bit fault tolerant ALU. The scheme uses BCH codes for detecting and correcting 5-bit error in any position of its 32-bits input register. Each encoder and decoder takes 63 clock cycles to compute the result that introduces more delay to the circuit. Faults within the ALU cannot be detected by this scheme.

Area and time efficient self-checking adders have been proposed recently using two rail codes [18], but the circuits can't be used in ALU because the shifter and logic unit have to be encoded using different codes, and thus require different checkers as well. This not only increases the complexity of the system, but also the cost as well.

In this thesis we present an AUED method for detecting errors in ALU using Scalable Error Detecting Codes (SEDC) [19]. Unlike BCP [5], this scheme generates the check bits without using the internally generated carries which is the main reason why this scheme is more area and delay efficient than the BCP scheme. With 100% fault coverage against all unidirectional errors, SEDC scheme also provides 82% fault coverage against all other errors that emerge due to single faults in the ALU. SEDC is easily scalable for any number of input bits 'n' while latency of SEDC encoded ALU remains constant. Unlike residual codes, here we use only one type of error detection scheme i.e., SEDC scheme for entire design of ALU, that also simplifies the overall chip design. The area and delay efficient, scalable TSC checker for SEDC scheme is also presented in this paper which further reduce the area of overall system. Although, our coding scheme have bigger code length than Berger codes, but the area efficient TSC SEDC checker requires less area than the TSC Berger checker. The prototype SEDC based ALU system is implemented on FPGA platform which exploits its reconfiguration feature to mitigate permanent errors.

#### **III.** Scalable Error Detection Coding Scheme

Scalable Error Detection Coding scheme [19] is formulated and designed in such a way that only area is scaled, while latency depends on a small portion of the input data (explained later).

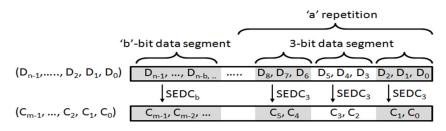

For any input binary data D of length n-bits represented as  $(D_{n-1}, ..., D_2, D_1, D_0)$  with  $D_i \in \{0, 1\}$  for  $0 \le i \le n-1$ , two parameters 'a' and 'b' are computed using (1), where parameter 'a' can only be a positive integer, and parameter 'b' can take values only from 2, 3 or 4.

$$a = \frac{n - \max(b)}{3} \tag{1}$$

Satisfying the condition for parameter 'a', the maximum possible value for parameter 'b' is selected. The length of SEDC code C represented as  $(C_{m-1}, ..., C_j, ..., C_2, C_1, C_0)$  with  $C_j \in \{0, 1\}$  for  $0 \le j \le m-1$ , is then computed as per (2).

$$m = [log_2(n+1-3a)] + 2a \tag{2}$$

After computing the values for parameters 'a' and 'b', the SEDC code 'C' for input binary data 'D' is computed. SEDC is designed to generate codes basically for 2-, 3-, and 4-bit data and accordingly referred to as  $SEDC_2$ ,  $SEDC_3$  and  $SEDC_4$  scheme, respectively. It is then extended for any integer values of n, as shown in Fig. 3.1.

Figure 3.1 Data partitioning and encoding using SEDC scheme for given data word

Next, we will discuss the mathematical foundations of  $SEDC_2$ ,  $SEDC_3$  and  $SEDC_4$  schemes with logical explanations about their error detecting capabilities.

#### A. SEDC<sub>2</sub> code

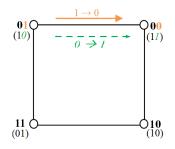

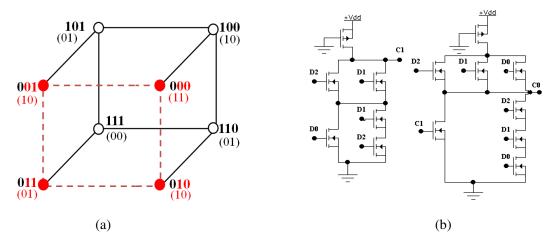

Fig. 3.2 gives a 2-D square illustration of SEDC<sub>2</sub> scheme where nodes represent data words

and their corresponding code words are written in brackets.

The SEDC coding scheme assigns code words to different data words with a unique criteria. Whenever there is a change of bit (or bits) in data word from '1'  $\rightarrow$  '0' (shown with bold arrow in Fig. 3.2), the change is reflected on code word in opposite way, i.e., the code changes from '0'  $\rightarrow$  '1'(shown with dashed arrow in Fig. 3.2), and vice versa. In general, when the weight of data word increases, the weight of its SEDC code word decreases and vice versa. Equation (3) is used to assign 2-bit code words 'C<sub>1</sub>C<sub>0</sub>' to the 2-bit data words D<sub>1</sub>D<sub>0</sub>. C<sub>1</sub>C<sub>0</sub> can also be used interchangeably; this results in another variant of SEDC<sub>2</sub> code.

$$[C_1:C_0] = [NAND(D_1, D_0): XNOR(D_1, D_0)]$$

(3)

$SEDC_2$  is the basic coding scheme and is embedded in  $SEDC_3$  and  $SEDC_4$  to detect all unidirectional errors in 3-bit and 4-bit data, as shown later. This ability of scaling codes is not present in any other coding scheme.

Figure 3.2 2D illustration of SEDC<sub>2</sub> scheme

#### B. SEDC<sub>3</sub> code

SEDC<sub>3</sub> code for 3-bit data is computed as per (4).

$$(\mathbf{C}_1, \mathbf{C}_0) = \begin{cases} \text{SEDC}_2(\mathbf{D}_1, \mathbf{D}_0), & \text{if } \mathbf{D}_2 = 0\\ 1 \text{'s complement}(\text{SEDC}_2(\overline{\mathbf{D}_1}, \overline{\mathbf{D}_0})), & \text{if } \mathbf{D}_2 = 1 \end{cases}$$

$$(4)$$

Fig. 3.3.(a) shows a 3-D cube illustrating the unidirectional error detection mechanism of SEDC<sub>3</sub> codes. Same notations are used in Fig. 3.3.(a) as in Fig. 3.2. The dashed side of the cube represents the embedded SEDC<sub>2</sub> coding scheme in SEDC<sub>3</sub>. Note that when there is a 2-bit unidirectional change in data word '001' to '111' (two MSB's changing from '00' to '11'), the

code changes in the opposite direction (MSB of the code changes from '1' to '0').

The first four code words for  $SEDC_3$  are same as  $SEDC_2$  as shown in Fig. 3. 3(a) (with dashed side). The remaining four code words are generated by the following steps:

1) Invert all the 3-bit data bits (we take '100' $\rightarrow$ '011').

2) Find the SEDC<sub>2</sub> code word corresponding to the inverted data resulting from step 1 ('011' $\rightarrow$ '01').

3) Now invert the SEDC<sub>2</sub> code word which came from step 2 ('01' $\rightarrow$ '10').

4) The inverted  $SEDC_2$  code word resulted in step 3 becomes the code word for the data word selected in step 1.

Figure 3.3 (a) 3D illustration of SEDC<sub>3</sub> scheme (b) SEDC<sub>3</sub> circuit

Any two data words  $D_A$  and  $D_B$  such that  $D_B$  can be converted to  $D_A$  by just changing the 1's  $\rightarrow$  0's or 0's  $\rightarrow$  1's, are assigned unique code word by above shown steps, hence making it possible to detect all unidirectional errors.

#### C. SEDC<sub>4</sub> code

SEDC<sub>4</sub> code for 4-bit data is formulated as per (5).

$$[C_{2}: (C_{1}, C_{0})] = [NOT (D_{3}): SEDC_{3} (D_{2}, D_{1}, D_{0})]$$

(5)

MSB of the code word is completely dependent upon MSB of the data word for SEDC<sub>4</sub>; hence any change in the MSB of the data word is detected. While the rest of the three data bits

are encoded using same SEDC<sub>3</sub> scheme.

In general, for SEDC<sub>n</sub>, the n-bit binary data is grouped into one 'b'-bit segment and 'a' number of 3-bit segments, and then these segments are encoded using SEDC<sub>b</sub> and 'a' number of SEDC<sub>3</sub> modules in parallel, as shown in Fig. 3.1. Small code words are produced from 3-bit and b-bit data segments for error detection. It is noteworthy that each group of data segment and corresponding code segment is independent to each other. This independency makes our scheme scalable.

We could partition to get Berger codes in parallel; however it requires more area than SEDC scheme. For instance, a 3-bit input SEDC circuit shown in Fig. 3.3.(b) can be implemented with 14 MOS transistors, while 3-input one's counter is implemented with a full adder that contains 28 MOS transistors [20].

#### IV. Introduction to Overall System

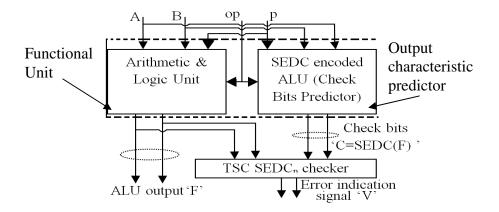

The general block diagram of SEDC based error detecting ALU is depicted in Fig. 4.1. [19]. SEDC is a concurrent error detection (CED) scheme which requires a separate encoded module, like the one proposed in [21]. Inputs are simultaneously applied to the functional unit (in our case ALU) and output characteristic predictor circuit (in our case SEDC encoded ALU or SEDC check bits predictor). TSC SEDC checker validates the output of both ALU and SEDC encoded ALU.

Figure 4.1 General model for SEDC based Self-checking ALU

#### A. Arithmetic and Logic Unit

The ALU generates the normal output 'F(A, B, op, p)' by taking the inputs 'A', 'B', 'op' and 'p'. The ALU circuit is capable of performing four basic operations, namely Boolean Operation of two n-bit operands, n-bit Shift/Rotate Operation, n-bit Add/Subtract Operation and n-bit Compare Operation (abbreviated as BO, SRO, ASO and CO respectively throughout the thesis).

Input 'op' is designated to specify particular Arithmetic or Logic Operation (like Add/Sub, Shift or any Boolean Operation). To provide the input shift bit 's<sub>i</sub>' for shift operation, or carry input 'c<sub>in</sub>' for Add/Subtract operation, 1-bit input 'p' is used.

#### **B. SEDC encoded ALU**

SEDC encoded ALU or SEDC check bits predictor is designed in such a way that it generates the corresponding SEDC check bits 'C = SEDC(F)' using the same inputs 'A', 'B', 'p' and 'op', in parallel. For designing this SEDC encoded ALU, we generated truth tables with inputs A, B, op and p, while the output equals to 'C = SEDC (F)', using Logic Friday software.

Similar to the ALU, SEDC encoded ALU comprises of SEDC encoded BO Unit, SEDC encoded SRO Unit, SEDC encoded ASO Unit and SEDC encoded Compare Unit. To switch between different operations, input 'op' is used. One can observe from Fig. 4.1, that unlike BCP ALU [5], SEDC encoded ALU does not use the internally generated carries.

#### C. TSC SEDC checker

A totally self-checking (TSC) SEDC checker is used to validate the ALU output 'F' with its corresponding SEDC encoded ALU output 'C'. A 2-bit error signal 'V' is generated if 'F' and 'C' do not correspond to each other (i.e.,  $C \neq SEDC$  (F)). As the checker is TSC, hence it has the ability to detect or safely hide its own error. The checker also exhibits scalability, i.e., the checker can be designed for any number of input bits with little increment in hardware while the latency remains constant.

#### V. Formulation of SEDC encoded ALU

In this chapter we will discuss the formulation of each SEDC encoded ALU operation (Boolean, shift/rotate and add/subtract operation, compare operation with some examples).

#### A. 2-, 3- and 4-bit SEDC encoded Boolean Operation Unit

In Table 5-1 [19], we list the logic equations to implement 2-bit SEDC encoded BO Unit. The symbol 'opBO' is equivalent to 'op' in Fig. 4.1. A total of 16 Boolean logic operations can be performed by changing input 'opBO'.

| Operations           | opBO | 2-bit SEDC Encoded Boolean Operations                                                          | A <sub>3</sub> / | <b>B</b> <sub>3</sub> / | S9/      |

|----------------------|------|------------------------------------------------------------------------------------------------|------------------|-------------------------|----------|

|                      |      | $(C_{1(2BIT)}, C_{0(2BIT)}) = SEDC_2 (A, B, OPBO)$                                             | $A_2$            | $B_2$                   | $S_{10}$ |

| Logic 0              | 0    | SEDC <sub>2</sub> (00)                                                                         | Х                | Х                       | 0        |

| A NOR B              | 1    | $\text{SEDC}_2(\bar{A}) + \text{SEDC}_2(\bar{B}) - \text{SEDC}_2(\bar{A} \text{ OR } \bar{B})$ | 0                | 0                       | 1        |

| $\bar{A}$ AND B      | 2    | $\text{SEDC}_2(\bar{A}) + \text{SEDC}_2(B) - \text{SEDC}_2(\bar{A} \text{ OR } B)$             | 0                | 1                       | 1        |

| Ā                    | 3    | $\text{SEDC}_2(\bar{A})$                                                                       | 0                | Х                       | 1        |

| A AND $\overline{B}$ | 4    | $SEDC_2(A) + SEDC_2(\overline{B}) - SEDC_2(AOR\overline{B})$                                   | 1                | 0                       | 1        |

| $\overline{B}$       | 5    | $\text{SEDC}_2(\overline{B})$                                                                  | Х                | 0                       | 1        |

| A XOR B              | 6    | $SEDC_2(A) + SEDC_2(B) - (2 \times SEDC_2(A.B)) +$                                             | 0                | 1                       | 1        |

|                      |      | 3                                                                                              | 1                | 0                       | 1        |

| A NAND B             | 7    | $\text{SEDC}_2(\bar{A}) + \text{SEDC}_2(\bar{B}) - \text{SEDC}_2(\bar{A}.\bar{B})$             | 1                | 1                       | 0        |

| A AND B              | 8    | $SEDC_2(A) + SEDC_2(B) - SEDC_2(A \text{ OR } B)$                                              | 1                | 1                       | 1        |

| A XNOR B             | 9    | $\text{SEDC}_2(\bar{A}) + \text{SEDC}_2(B) - (2 \times \text{SEDC}_2(\bar{A} \cdot B))$        | 0                | 0                       | 1        |

|                      |      | + 3                                                                                            | 1                | 1                       | 1        |

| В                    | 10   | SEDC <sub>2</sub> (B)                                                                          | Х                | 1                       | 1        |

| $\overline{A}$ OR B  | 11   | $\text{SEDC}_2(\bar{A}) + \text{SEDC}_2(B) - \text{SEDC}_2(\bar{A} \cdot B)$                   | 1                | 0                       | 0        |

| А                    | 12   | SEDC <sub>2</sub> (A)                                                                          | 1                | Х                       | 1        |

| A OR $\overline{B}$  | 13   | $SEDC_2(A) + SEDC_2(\overline{B}) - SEDC_2(A \cdot \overline{B})$                              | 0                | 1                       | 0        |

| A OR B               | 14   | $SEDC_2(A) + SEDC_2(B) - SEDC_2(A \cdot B)$                                                    | 0                | 0                       | 0        |

| Logic 1              | 15   | SEDC <sub>2</sub> (11)                                                                         | Х                | Х                       | 1        |

Table 5-1. Logic for 2-bit SEDC encoded BO Unit

The '*SEDC*<sub>2</sub>' symbol mentioned in Table 5-1 generate the *SEDC*<sub>2</sub> check bits ' $C_{1(2bit)}C_{0(2bit)}$ ' of the 2-bit input operands 'A' and 'B'. '2 x *SEDC*<sub>2</sub>' denote the one bit left shifted result after taking *SEDC*<sub>2</sub> of the operands, with '0' as the input shift bit. Other symbols like '+' and '-' represent the normal add and subtract operations. " $\overline{A}$ " shows the inverted A, while 'AND', 'OR', 'XOR', 'NAND' and 'NOR' are the normal 2 operand logic gate operations. For example, if the value of 'opBO' is 6, then the output of the ALU is normal XOR value of 'A'

and 'B' while output of the SEDC encoded ALU is computed by the corresponding equation from Table 5-1. Unlike BCP ALU [5], Table 5-1 don't contain any signal (Carry out, internally generated carries etc) that is being generated by normal ALU. This makes SEDC encoded ALU faster than BCP ALU. Following example illustrates the 2-bit SEDC encoded XOR operation.

*Example 1:* Let A = 01, B = 10, opBO = 0110 (XOR)

$$\Rightarrow$$

A AND B = 00; SEDC<sub>2</sub>(A) = 10, SEDC<sub>2</sub>(B) = 10, SEDC<sub>2</sub>(A AND B) = 11;

$$\Rightarrow$$

2x*SEDC*<sub>2</sub>(A AND B) = 110;

$\Rightarrow SEDC_2(A) + SEDC_2(B) - \{2xSEDC_2(A \text{ AND } B)\} + 3 = 001$

Discarding the MSB, the remaining two LSBs '01' are the  $SEDC_2$  check bits for XOR operation between 'A' and 'B', which can be verified from (3).

For scaling 2-bit SEDC encoded BO unit to 3-bit, 'opBO', 'A<sub>2</sub>' and 'B<sub>2</sub>' signals are encoded to generate 'S<sub>9</sub>', using Table 5-1 (where 'A<sub>2</sub>' and 'B<sub>2</sub>' are the MSB's of the 3-bit input operands 'A' and 'B' respectively). Replacing 'S<sub>Q</sub>' with 'S<sub>9</sub>' in (6), will yield the SEDC<sub>3</sub> check bits  $C_{1(3bit)}C_{0(3bit)}$ .

$$(C_{1(3bit)}, C_{0(3bit)}) = \begin{cases} (C_{1(2bit)}, C_{0(2bit)}) - 1 & \text{if } S_Q = 1 \\ (C_{1(2bit)}, C_{0(2bit)}) & \text{otherwise} \end{cases}$$

(6)

Similarly, (7) & (8) are used for scaling 3-bit SEDC encoded BO unit to 4-bit unit. Here signals 'opBO', 'A<sub>3</sub>' and 'B<sub>3</sub>' are encoded to generate 'S<sub>10</sub>' using Table 5-1, and depending upon 'S<sub>10</sub>', the output *SEDC*<sub>4</sub> code C<sub>2(4bit)</sub>C<sub>1(4bit)</sub>C<sub>0(4bit)</sub> is obtained.

$$C_{2(4\text{bit})} = \begin{cases} 1 & \text{if } S_{10} = 0\\ 0 & \text{otherwise} \end{cases}$$

(7)

$$(C_{1(4bit)}, C_{0(4bit)}) = SEDC_3(A_{(3bit)}, B_{(3bit)}, opBO)$$

(8)

#### B. 2-, 3- and 4-bit SEDC encoded Shift/Rotate Unit

The SEDC check of the result of a shift/rotate operation is simply the SEDC check of the operand, since no information bit is discarded except for their position. The logic shift

operation involves the ' $s_i$ ' bit (equivalent to 'p' in Fig. 4.1) as input shift bit. Table 5-2 tabulates the logic of 2-bit SRO unit [19].

| Operations     | opSR | 2-bit SEDC Shift/Rotate Operations                            |  |  |

|----------------|------|---------------------------------------------------------------|--|--|

|                |      | $(C_{1(2bit)}, C_{0(2bit)}) = SEDC_2(A(A_1, A_0), s_i, opSR)$ |  |  |

| Shift Left A   | 00   | $SEDC_2([A_0 s_i])$                                           |  |  |

| Shift Right A  | 01   | $SEDC_2([s_i A_1])$                                           |  |  |

| Rotate Left A  | 10   | $SEDC_2(A)$                                                   |  |  |

| Rotate Right A | 11   | SEDC <sub>2</sub> (A)                                         |  |  |

Table 5-2. Logic for 2-bit SEDC encoded SRO Unit

The circuit is able to perform same operations given in [5] that are, shift left, shift right, rotate left and rotate right on any 2-bit operand 'A' and generate its 2-bit SEDC code. Following is the example to illustrate the 2-bit SEDC encoded shift/rotate operation.

*Example 2:* Let A = 01,  $s_i = 1$ , opSR = 01 (shift right);

$$\Rightarrow [s_i A_1] = 10; \qquad (normal shift output)$$

$$\Rightarrow SEDC_2([s_i A_1]) = 10 \qquad (SEDC encoded output)$$

For scaling 2-bit SEDC encoded SRO unit to 3-bit unit, we replaced  $S_Q$  with  $S_1$  in (6), while for scaling 3-bit SRO unit to 4-bit unit we used (9) & (10). Signal 'sibit' and  $S_1$  are generated using primary inputs opSR, A and si, whose logic equations are given in Table 5-2.

$$(C_{1(4bit)}, C_{0(4bit)}) = SEDC_{3}(A(A_{2}, A_{1}, A_{0}), sibit, opSR)$$

(9)

$$C_{2(4bit)} = \begin{cases} NOT A_{2}, \text{ if } opSR = 0\\ NOT si, \text{ if } opSR = 1\\ NOT A_{2}, \text{ if } opSR = 2\\ NOT A_{0}, \text{ if } opSR = 3 \end{cases}$$

(10)

#### C. 2-, 3- and 4-bit SEDC encoded Add/Subtract Unit

The SEDC check of the result of an add/subtract operation is simply the SEDC check of the normal add/subtract result, as formulated in (11) & (12) [19].

$$C_{1(2bit)}, C_{0(2bit)} = SEDC \left\{ A \oplus (B \oplus opAS) \oplus (C_{in} \oplus opAS) \right\}$$

(11)

$$C_{c(2bit)} = SEDC\{A \oplus (B \oplus opAS)\}(C_{in} \oplus opAS) + A(B \oplus opAS)$$

(12)

The 'opAS' here corresponds to the input 'op', and ' $C_{in}$ ' corresponds to 'p' in Fig. 4.1.  $C_{c(2bit)}$  and  $C_{1(2bit)}C_{0(2bit)}$  are SEDC check bits for output carry and sum, respectively. Example 3 shows the SEDC check bit generation for 2-bit add operation.

*Example 3:* Let A = 01, B = 10,  $C_{in} = 1$ , opAS = 0;

$\Rightarrow C_{out} = 1, \qquad A + B + C_{in} = Sum = 00;$  $\Rightarrow SEDC_2 C_{out} = 0, \qquad SEDC_2 Sum = 11;$

Here again, for scaling 2-bit SEDC encoded Add unit to 3-bit unit, (6) is used to generate check bits  $C_{1(3bit)}C_{0(3bit)}$  corresponding to the output *sum* of the ALU, by replacing S<sub>Q</sub> with S<sub>15</sub>. The logic equations that generate check bit for carry out signal  $C_{c(3bit)}$  and S<sub>15</sub> signal are given in Table 5-3.

Similarly, (13) & (14) are used to generate the check bits  $C_{2(4bit)}C_{1(4bit)}C_{0(4bit)}$ , corresponding to output *sum* of the 4-bit SEDC encoded ALU, while the logic equations for carry out signal  $C_{c(4bit)}$  and  $S_{17}$  signal are given in Table 5-3.

$$C_{2(4bit)} = \begin{cases} \text{NOT } C_{c(2bit)}, & \text{if } S_{17} = 1\\ C_{c(2bit)}, & \text{otherwise} \end{cases}$$

(13)

$(C_{1(4bit)}, C_{0(4bit)}) = (A_{(3bit)}, B_{(3bit)}, C_{in}, opAS)$ (14)

The three SEDC encoded operation units compute the SEDC check bits independent of the internally generated carries from the normal ALU, which reduce the overall latency of the system.

Table 5-3. Logic equations for S<sub>1</sub>, sibit, S<sub>14</sub>-S<sub>15</sub> signals

| $S_1 = (opSR_1')(opSR_0)(A_2) + (opSR_1')(opSR_0')(A_1)$                                                         |

|------------------------------------------------------------------------------------------------------------------|

| $sibit = (opSR_0)(A_3) + (opSR_0')(s_i)$                                                                         |

| $S_{14} = C_{c(3bit)} = (B_2')(C_{c(2bit)}) + (A_2')(B_2')(C_{c(2bit)}') + (A_2')(B_2)(C_{c(2bit)})$             |

| $S_{15} = (A_2)(B_2)(C_{c(2bit)}) + (A_2)(B_2)(C_{c(2bit)}) + (A_2)(B_2)(C_{c(2bit)}) + (A_2)(B_2)(C_{c(2bit)})$ |

| $S_{16} = C_{c(4bit)} = (A_3')(B_3') + (A_3')(C_{c(3bit)}) + (B_3')(C_{c(3bit)})$                                |

| $S_{17} = A_3' B_3 + A_3 B_3'$                                                                                   |

Equations in Table 5-3 [19] are formulated by inputting the logic tables in Logic Friday software and then minimizing them to generate logic equations. All the logic equations uses

primary inputs 'A', 'B', 'p' and 'op' to compute the SEDC check bits of a particular Arithmetic and Logic operation.

All the circuits are implemented using combinational logic. These circuits can also work for 1-bit input data. The only change to made is; take the LSB of the SEDC Code ( $C_0$ ) rather than taking both  $C_1C_0$  bits.

#### D. 2-, 3- and 4-bit SEDC encoded Compare Unit

The Compare unit takes in only two operands A & B, and can perform three operations, that are, A greater than B, A is equal to B, and A is smaller than B. Particular operation can be selected using the input op. Table 5-4 enlists the  $SEDC_2$  code of the two input compare operation.

| Table 3-4. Logic for 2-bit SEDC encoded Compare Onit |    |                        |  |  |  |

|------------------------------------------------------|----|------------------------|--|--|--|

| Operations opCC 2-bit SEDC Compare Operations        |    |                        |  |  |  |

| $(C_{1(2bit)}, C_{0(2bit)}) = SEDC_2(A(A_1, A_2))$   |    |                        |  |  |  |

|                                                      |    | $B(B_1, B_0), opCC)$   |  |  |  |

| A > B                                                | 00 | SEDC <sub>2</sub> (00) |  |  |  |

| A == B                                               | 01 | SEDC <sub>2</sub> (01) |  |  |  |

| A < B                                                | 11 | SEDC <sub>2</sub> (11) |  |  |  |

Table 5-4. Logic for 2-bit SEDC encoded Compare Unit

For scaling 2-bit unit to 3- (e = 2) and 4-bit (e = 3) unit, equation (15) is generally used.  $[C_{1(e+1-bit)}, C_{0(e+1-bit)}] = [\{(A_e + C_{1(e-bit)}).\overline{B_e} + A_e.C_{1(e-bit)}\}, \{(A_e \oplus B_e) + C_{0(e-bit)}\}]$ (15)

#### VI. Scaling SEDC encoded ALU for n-bit Input

As discussed in chapter II, SEDC scheme is made for 2-, 3- and 4-bit inputs. For n-bit input, combination of these 2-, 3- and 4-bit input schemes are used, denoted as  $SEDC_2$ ,  $SEDC_3$  and  $SEDC_4$  respectively. Following we give logic and examples for designing n-bit SEDC encoded BO, SRO and ASO units using their respective 2-, 3- and 4-bit modules.

#### A. n-bit SEDC encoded Add/Subtract Unit

The SEDC<sub>n</sub> check bits (C<sub>m</sub>) have two parts; {C<sub>m-1</sub>, C<sub>m-2</sub>,...,C<sub>m-L</sub>} generated by b-bit SEDC encoded BO with input operands {A<sub>n-1</sub>, A<sub>n-2</sub>,..., A<sub>n-b</sub>}, {B<sub>n-1</sub>, B<sub>n-2</sub>,..., B<sub>n-b</sub>}, opBO, and {C<sub>m-(2xk)-L-1</sub>, C<sub>m-(2xk)-L-2</sub>} generated by sets of 3-bit SEDC encoded BO on inputs {A<sub>nn-1</sub>, A<sub>nn-2</sub>, A<sub>nn-3</sub>}, {B<sub>nn-1</sub>, B<sub>nn-2</sub>, B<sub>nn-3</sub>}, opBO. For calculating values of nn, k and L, (16)-(18) [19] can be used.

$$nn = n - (3k) - b \tag{16}$$

$$k = 0 \text{ to } (a - 1)$$

(17)

$$L = [log_2\{n+1-(3a)\}]$$

(18)

*Example 5:* Let A and B contains 8-bit each;

$\Rightarrow$  b = 2, a = 2 and m = 6 {from (1) & (2)}

$$\Rightarrow$$

k = 0 to 1, nn = 6, 5 and L = 2. {from (16)-(18)}

So we generate  $(C_5, C_4)$  using one 2-bit SEDC encoded BO unit  $(SEDC_2)$  with inputs  $(A_7, A_6)$ ,  $(B_7, B_6)$  while  $(C_3, C_2)$ ,  $(C_2, C_0)$  are generated using two 3-bit SEDC encoded BO units  $(SEDC_3)$  with inputs  $(A_5, A_4, A_3)$ ,  $(B_5, B_4, B_3)$  &  $(A_2, A_1, A_0)$ ,  $(B_2, B_1, B_0)$  respectively. Input 'opBO' being the common input to all of the three SEDC encoded modules.

#### B. n-bit SEDC encoded Add/Subtract Unit

Similar to n-bit BO operation unit, the logic to implement n-bit SEDC encoded SRO unit is given in Table 6-1 [19]. Again the modules are split into b-bit and 3-bit modules for generating the SEDC code. For 8-bit SEDC encoded SRO unit, values of a, b, m, k and L remains same as in Example 5. Check bits ( $C_5$ ,  $C_4$ ) are generated by 2-bit SEDC encoded SRO unit using ( $A_7$ ,  $A_6$ ), ( $B_7$ ,  $B_6$ ) and sibit<sub>1</sub> as inputs while ( $C_3$ ,  $C_2$ ) and ( $C_1$ ,  $C_0$ ) are generated by two 3-bit SEDC encoded SRO units with inputs ( $A_5$ ,  $A_4$ ,  $A_3$ ), ( $B_5$ ,  $B_4$ ,  $B_3$ ), sibit<sub>2</sub> and ( $A_2$ ,  $A_1$ ,  $A_0$ ), ( $B_2$ ,  $B_1$ ,  $B_0$ ), sibit<sub>2</sub>' respectively. The sibit<sub>2</sub>' is computed the same way as sibit<sub>2</sub> but with changed values of 'k'. The logic to generate sibit<sub>1</sub> and sibit<sub>2</sub> signals is also given in Table 6-1.

| b-bit SEDC encoded SRO unit with inputs ((A <sub>n-1</sub> , A <sub>n-2</sub> ,A <sub>n-b</sub> ), sibit <sub>1</sub> , opSR) |      |         |                                                                                                                                                                  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Operations                                                                                                                    |      | opSR    | sibit <sub>1</sub>                                                                                                                                               |  |  |  |

| Shift/Rotate Left A                                                                                                           |      | X0      | A <sub>n-b-1</sub>                                                                                                                                               |  |  |  |

| Shift Right A                                                                                                                 |      | 01      | Si                                                                                                                                                               |  |  |  |

| Rotate Right A                                                                                                                |      | 11      | $A_0$                                                                                                                                                            |  |  |  |

| 3-bit SEDC encoded SRO unit with inputs ((Ann-1, Ann-2, Ann-3), sibit2, opSR)                                                 |      |         |                                                                                                                                                                  |  |  |  |

| Operations                                                                                                                    | opSR | k       | sibit <sub>2</sub>                                                                                                                                               |  |  |  |

| Shift Left A                                                                                                                  | 00   | = (a-1) | Si                                                                                                                                                               |  |  |  |

| Shift Left A                                                                                                                  | 00   | ≠ (a-1) | $\frac{sibit_{I}}{A_{n-b-1}}$ $\frac{A_{0}}{A_{0}}$ $A_{nn-3}), sibit_{2}, opSR)$ $\frac{sibit_{2}}{S_{i}}$ $\frac{A_{n-b-(3x(k+1)-1}}{A_{n-b-(3xk)}}$ $A_{nsb}$ |  |  |  |

| Shift/Rotate Right A                                                                                                          | 01   | Х       | A <sub>n-b-(3xk)</sub>                                                                                                                                           |  |  |  |

| Dototo Loft A                                                                                                                 | 10   | = (a-1) | A <sub>msb</sub>                                                                                                                                                 |  |  |  |

| Rotate Left A                                                                                                                 | 10   | ≠(a-1)  | $A_{n-b-(3x(k+1))-1}$                                                                                                                                            |  |  |  |

Table 6-1. Logic for scaling n-bit SEDC encoded SRO unit

#### C. n-bit SEDC encoded Add/Subtract Unit

Table 6-2 [19] list the logic to design n-bit SEDC encoded ASO unit. Care must be taken to connect carry in and carry out signals between a b-bit and 3-bit SEDC encoded ASO units. Also there is a requirement of two extra XOR gates for inverting B and Cin bits (for subtraction operation).

| Table 6-2. Logic for scaling n-bit SEDC encoded ASO unit |                          |                                                      |                                            |                |  |  |

|----------------------------------------------------------|--------------------------|------------------------------------------------------|--------------------------------------------|----------------|--|--|

| b-bit SEDC encoded ASO unit                              |                          |                                                      |                                            |                |  |  |

| Inputs = $((A_{n-1}, A_{n-2},$                           | ., A <sub>n-b</sub> ), ( | <b>B</b> <sub>n-1</sub> , <b>B</b> <sub>n-2</sub> ,, | $\mathbf{B}_{n-b}$ ), $\mathbf{C}_{in1}$ , | opAS)          |  |  |

| Operations                                               | opAS                     | а                                                    | $C_{in1}$                                  | В              |  |  |

| $A + B + C_{in}$                                         | 0                        | = 0                                                  | C <sub>in</sub>                            | В              |  |  |

| $A + B + C_{in}$                                         | 0                        | $\neq 0$                                             | $C_k$                                      |                |  |  |

|                                                          | 1                        | 0                                                    | $\overline{Cin}$                           | $\overline{B}$ |  |  |

| $A - B - C_{in}$                                         | 1                        | $\neq 0$                                             | $\overline{Ck}$                            | В              |  |  |

| $(C_{K}, C_{Sm-L-1},, C_{Sm-C})$                         | $_{2xL)-L-2} = 3$        | 3-bit SEDC er                                        | coded ASC                                  | ) unit         |  |  |

| Inputs = $((A_{nn-1}, A_{nn-2},$                         |                          |                                                      |                                            |                |  |  |

| Operations                                               | opAS                     | k                                                    | $C_{in2}$                                  | В              |  |  |

| $A + B + C_{in}$                                         | 0                        | = (a-1)                                              | C <sub>in</sub>                            | В              |  |  |

| $A + B + C_{in}$                                         | 0                        | ≠(a-1)                                               | C <sub>k+1</sub>                           | D              |  |  |

|                                                          | 1                        | = (a-1)                                              | $\overline{Cin}$                           | $\overline{B}$ |  |  |

| $A - B - C_{in}$                                         | 1                        | ≠(a-1)                                               | $\overline{C_k + 1}$                       | В              |  |  |

#### C. n-bit SEDC encoded Compare Unit

Equation (16)-(18) can be used in similar way to partition the data as described earlier. For designing n-bit SEDC encoded Compare unit, Equation (15) can be utilized. The value of 'e' should be equal to 'n-1'.

#### VII. TSC SEDC checker

In this chapter we will discuss the basic difference between a SEDC code checker and a Berger code checker. With introduction to '10' coding, we will explain the logic equations and MOS level circuit diagrams to implement TSC SEDC checker. We will also show the scaling of TSC SEDC checker to any number of input bits 'n' using the basic 2-, 3- and 4-bit TSC SEDC checkers.

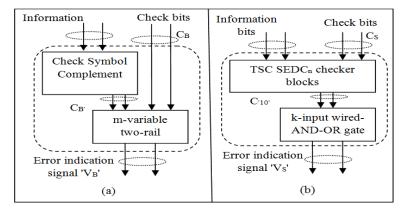

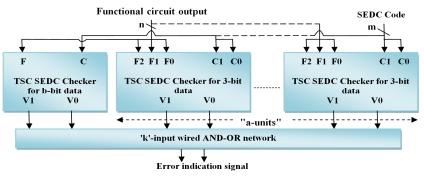

#### A. Difference between SEDC and Berger code checker

Close inspection of Fig. 7.1.(a) and Fig.7.1.(b) reveals that Berger code checker differ SEDC checker by two modules namely; the check bit complement generator which generates the bit by bit complement of the check bits and a tree of two rail checker [7]. As the complement generator generates the bit by bit complement, in other words, Berger checker encodes the n-bit 'F' and m-bit pre-computed check bits into two rail codes. The two rail codes are then checked using tree structure [22]. If we partition the Berger codes in a similar way as we do with SEDC, then this two rail code length will increase, causing the depth of two rail checker tree to increase.

Figure 7.1 Architectures of TSC (a) Berger checker (b) SEDC checker

On the other hand, SEDC checker has distinct modules as shown in Fig.7.1.(b): the SEDC<sub>n</sub> checker and the wired AND-OR logic block. The SEDC<sub>n</sub> checker encodes the n-bit 'F' and m-bit 'C' into '10' codes. Table 7-1 [23]shows the '10' coding scheme for 1-information bit 'F<sub>0</sub>'

and 1-check bit 'C<sub>0</sub>', according to which the correct output code space is  $V_1V_0 = \{10\}$  only (that is why we named this encoding scheme as '10' encoding), while in two rail encoding the correct code space is  $V_1V_0 = \{01, 10\}$ . The benefit of '10' codes is that they can be checked using wired AND-OR circuits in parallel, while the two rail codes can only be checked using a tree of two rail checkers, which increases the overall delay if the length of check bits increases.

F<sub>0</sub> C<sub>0</sub>  $V_1$ Vo 0 0 1 1 0 1 0 1 1 0 1 0 0 0 1 1

**Table 7-1.** '10' Codes Table for one bit input (SEDC<sub>1</sub>)

#### B. Logic and circuits for TSC SEDC<sub>1</sub>, SEDC<sub>2</sub>, SEDC<sub>3</sub>, SEDC<sub>4</sub> and SEDC<sub>n</sub> checkers

The SEDC checker is also composed of one b-bit TSC SEDC checker and a-sets of 3-bit TSC SEDC checkers. These small checkers encodes 'F' and 'C' into '10' codes, rather than two rail codes. In the case of 1-, 2- and 3-bit TSC SEDC checkers, the output can be directly used as an error indication signal, but for n > 3, the outputs of smaller TSC SEDC checkers are converted to a 2-bit error signal using one level of wired-AND-OR gate. Subsections discuss the logic and circuit diagrams for primitive TSC SEDC checkers (SEDC<sub>1</sub>, SEDC<sub>2</sub>, SEDC<sub>3</sub> and SEDC<sub>4</sub> checkers) which can be used to scale the TSC SEDC checker to a n-bit TSC SEDC checker.

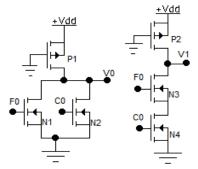

1. TSC SEDC<sub>1</sub> checker

Figure 7. 2 MOS circuit for TSC SEDC1 Checker

Fig. 7.2 shows the pseudo nMOS logic implementation of TSC SEDC<sub>1</sub> checker.

Table 7-1 shows the logic for 1-bit TSC SEDC (TSC SEDC<sub>1</sub> checker). Highlighted cases indicate the valid input code word (i.e., 10, 01) and the valid output code word (10).  $F_0$  denotes the 1-bit information word which is the output of ISG 'F' and C<sub>0</sub> denotes 1-bit SEDC check bit generated by SEDC Check Symbol Generator (SCSG) 'C'. V<sub>1</sub>V<sub>0</sub> is the 2-bit error indication signal of TSC SEDC checker 'V' [23].

### 2. TSC SEDC<sub>2</sub> checker

Equations (19) & (20) [23] are used to implement TSC SEDC<sub>2</sub> checker that generates the 2bit error signal  $V_1V_0$  (here "." & "+" denotes the normal AND & OR operations respectively). Again the correct output code space is {10}. Now C<sub>1</sub>C<sub>0</sub> denotes the SEDC check bits and F<sub>1</sub>F<sub>0</sub> are the information bits.

$$V_0 = \overline{(F_1 + F_0 + C_0)(C_1 + F_1 F_0 C_0)}$$

(19)

$$V_1 = \overline{C_1 \cdot (F_1 + F_0)(C_0 + F_1 F_0)}$$

(20)

The CMOS level design of TSC SEDC<sub>2</sub> checker requires only 9 extra MOS transistors to convert 1-bit SEDC checker circuit to 2-bit SEDC checker as shown in Fig. 7.3.

Checker

Figure 7. 4 Block diagram of 3-bit TSC SEDC checker

## 3. TSC SEDC<sub>3</sub> checker

Fig. 7.4 [23] shows the block diagram and the logic for 3-bit TSC SEDC checker. Three bit data  $F_2F_1F_0$  from ISG and 2-bit SEDC check bits  $C_1C_0$  from SCSG are first converted to  $F_1'F_0'$

and  $C_1'C_0'$  respectively and then they are checked using the same 2-bit TSC SEDC checker as shown in Fig. 7.4. When  $F_2$  bit is '1', the  $F_1F_0$  and  $C_1C_0$  are inverted, while if  $F_2$  is '0' then  $F_1F_0$  and  $C_1C_0$  remain same. As the outputs of XOR gates are fed to TSC SEDC<sub>2</sub> checker, hence any error in XOR gates is detected. This makes the overall 3-bit SEDC checker TSC.

### 4. TSC SEDC<sub>4</sub> checker

A 4-bit TSC SEDC checker consists of one TSC SEDC<sub>1</sub> checker and one TSC SEDC<sub>3</sub> checker as shown in Fig. 7.5 [23]. Both SEDC<sub>1</sub> and SEDC<sub>3</sub> checkers generate 2-bit output  $V_1V_0$ . As the valid code word is {10}, hence to make sure that both the checker units generate {10} output during error free operation, we 'AND'  $V_1$  output-bit of TSC SEDC<sub>1</sub> checker with  $V_1$  output-bit of TSC SEDC<sub>3</sub> checker. Also, we 'OR'  $V_0$  output-bits of both TSC SEDC checkers using wired logic gates. We checked and confirmed by fault simulation that wired-AND and wired-OR gates are also TSC for single faults (stuck-at-0, stuck-at-1, transistor-stuck-on and transistor-stuck-off).

Figure 7. 5 Block diagram of TSC SEDC<sub>4</sub> Checker

As compared to TSC Berger checker, SEDC checkers don't require tree of TSC two-rail checkers for comparison of check bits  $C_B$  with the predicted code bits  $C_B$ ', as shown in Fig. 7.1. The wired-AND and wired-OR circuitry show constant latency for any number of input bits, unlike the TRC tree.

### 5. TSC SEDC<sub>n</sub> checker

Similar to the SEDC code generator, TSC SEDC checker requires copies of 1-, 2- and 3-bit SEDC checkers depending upon the value of "a" and "b" (evaluated from (1)). For example, if

n=8 bits, then from (1), a = 2 and b = 2. This requires a TSC SEDC<sub>2</sub> checker and couple of TSC SEDC<sub>3</sub> checkers to realize an 8-bit TSC SEDC checker.

Circuit for wired-AND and wired-OR gates will also expand as "n" increases. For n = 8 bits, there will be total 3 TSC SEDC checkers with 2-bit output each. So a 3-input wired-AND and 3-input wired-OR gate is required to compare all the V<sub>1</sub> and V<sub>0</sub> bits. Fig. 7.6 [23] shows the block diagram of n-bit TSC SEDC checker.

Figure 7. 6 Block diagram of TSC SEDC<sub>n</sub> Checker

In general, for "n" bit input, there are "a+1" TSC SEDC checkers with 2-bit output each. So we require  $d = \{2x(a+1)\}$ -input wired-AND and wired-OR gates. With each increasing input to the wired-AND and wired-OR gates, one extra transistor is required by each of the wired-gates. Consequently, the circuit expands in width-wise fashion, and hence the latency of the wired logic remains constant for any value of "n".

Size of the load transistor driving these wired-AND and OR gates will also increase with increasing inputs. So we consider the maximum fan in of one gate equal to 4. For d > 4, an extra load transistor is connected in parallel. If "d" denotes the total number of inputs to the TSC checker then we require  $r = \lceil (k/4) \rceil$  load transistors. Total "d + r" number of transistors are required to implement the "d"-input wired AND-OR network with a constant latency of 1 transistor.

## VIII. Fault Coverage of SEDC encoded ALU

### A. Fault model

As discussed in Chapter III, SEDC scheme is an AUED scheme hence we assume that any single fault in ALU or SEDC encoded ALU causing a unidirectional change at their respective outputs, are detected by TSC SEDC checker. But there are some errors in ALU that result in bidirectional error at the output of ALU, and hence are not be detected by SEDC scheme. First we will explain the types of errors that can cause bi-directional change at the output of the ALU and then we will show that how much fault coverage SEDC scheme can provide against such errors.

### 1. Type 1 error

In typical ALU design, there is no distinction between the circuit that handles the arithmetic operations and that which handles the logic operations. Consequently, a single fault in carry propagation circuit may induce multiple random errors during the logic operations [5].

#### 2. Type 2 error

In a normal ripple carry adder, the carries and sum bits are not computed by independent circuits (i.e., the half-sum signals are used to compute the sum bits and also to propagate the carries). Thus an error to half-sum signal can modify both a carry  $c_i$  and an output sum  $s_i$  resulting in a bidirectional error.

#### 3. Type 3 error

The error in carry may propagate to other adder blocks, causing bidirectional errors at the output of ALU. As our scheme encodes 2-bit, 3-bit or 4-bit data segments separately, so we applied test vectors on a 2-bit, 3-bit and 4-bit carry ripple adder separately. We call each 2-bit, 3-bit and 4-bit carry ripple adder a "block". We applied stuck at '0' and stuck at '1' faults on  $1^{st}(C_1)$ ,  $2^{nd}(C_2)$  and  $3^{rd}(C_3)$  carry of ripple carry adder, one at a time, as shown in Fig. 8.1. We