F

e 2 b 0 r 1 u 9 a

r y

TDP heh srD ies ses

High-Performance Ternary Content Addressable Memory Architecture for FPGAs

Inayat Ullah

February 2019 Doctor of Philosophy Degree Thesis

# High-Performance Ternary Content Addressable Memory Architecture for FPGAs

Graduate School of Chosun University Department of Computer Engineering Inayat Ullah

# High-Performance Ternary Content Addressable Memory Architecture for FPGAs

February 2019

## Graduate School of Chosun University Department of Computer Engineering Inayat Ullah

# High-Performance Ternary Content Addressable Memory Architecture for FPGAs

FPGA 기반 고성능 TCAM 구조

Supervised by Professor Jeong-A Lee

A thesis submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Computer Engineering

25, February 2019

Graduate School of Chosun University Department of Computer Engineering Inayat Ullah

Collection @ chosun

## TABLE OF CONTENTS

| LI  | ST O | F ABB  | BREVIATIONS AND ACRONYMS                        | iv  |

|-----|------|--------|-------------------------------------------------|-----|

| AF  | BSTR | ACT    |                                                 | ix  |

| 한   | 글요   | 약      |                                                 | xii |

| I.  | INT  | RODU   | UCTION                                          | 1   |

|     | A.   | Backg  | ground                                          | 1   |

|     | B.   | Probl  | em Statement                                    | 3   |

|     | C.   | Motiv  | vations                                         | 6   |

|     | D.   | Thesi  | s Contributions                                 | 7   |

|     | E.   | Relate | ed Work                                         | 8   |

|     | F.   | Thesi  | s Organization                                  | 11  |

| II. | MU   | LTIPU  | MPING ENABLED MULTIPORTED SRAM-BASEI            | )   |

|     | TCA  | M AR   | RCHITECTURE                                     | 13  |

|     | A.   | Multi  | pumping-Enabled Multiported SRAM                | 13  |

|     |      | 1.     | Basic Idea                                      | 14  |

|     |      | 2.     | Proposed Partitioning of Traditional TCAM Table | 16  |

|     |      | 3.     | Basic Architecture of the Proposed TCAM Memory  | 17  |

|     |      | 4.     | Modular Architecture                            | 19  |

|     |      | 5.     | Effect of Multipumping SRAM on the Memory Usage |     |

|     |      |        | and Throughput                                  | 20  |

|     | B.   | Imple  | ementation Setup and Results                    | 20  |

|     | C.   | Perfo  | rmance Evaluation & Comparison                  | 21  |

|     |      | 1.     | SRAM Memory Utilization                         | 22  |

|         | 2.    | Throughput                                           | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 3.    | Performance per Memory                               | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| III.PRI | E-CLA | SSIFICATION- BASED ENERGY-EFFICIENT SRAM-            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BAS     | SED T | CAM ARCHITECTURE                                     | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| А.      | Prop  | osed Classification Scheme                           | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B.      | EE-T  | CAM Proposed Architecture                            | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| C.      | EE-T  | CAM FPGA Implementation & Results                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D.      | EE-T  | CAM Performance Evaluation & Comparison              | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 1.    | Scalability of EE-TCAM                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 2.    | Performance Trade-Off with Increase in the Number of |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |       | TCAM Sub-Tables (M)                                  | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 3.    | Power Consumption                                    | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 4.    | Power Consumption Per Performance Comparison         | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IV. DY  | NAMI  | CALLY RE-CONFIGURABLE ENERGY- AND                    | RAM-         28         28         28         34         34         37         38         1         38         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <tr< td=""></tr<> |

| RES     | SOUR  | CE- EFFICIENT TCAM ARCHITECTURE FOR FPGAS            | <b>4</b> 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A.      | Hard  | ware Architecture of Proposed TCAM: DURE             | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 1.    | Basic Idea                                           | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 2.    | Building Blocks of DURE on FPGA                      | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 3.    | Architecture of the Proposed DURE                    | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 4.    | Dynamic Update                                       | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B.      | FPG   | A Implementation and Results                         | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| C.      | DUR   | E Performance Evaluation and Comparison              | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

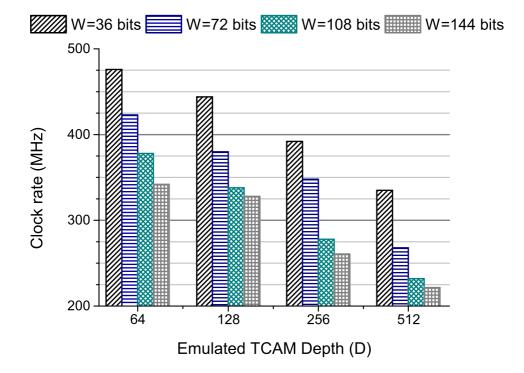

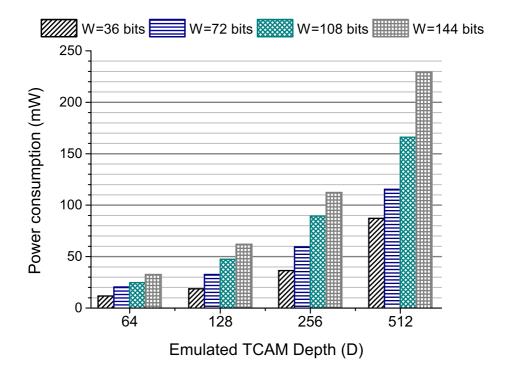

|         | 1.    | Scalability of DURE                                  | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 2.    | Search Latency                                       | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

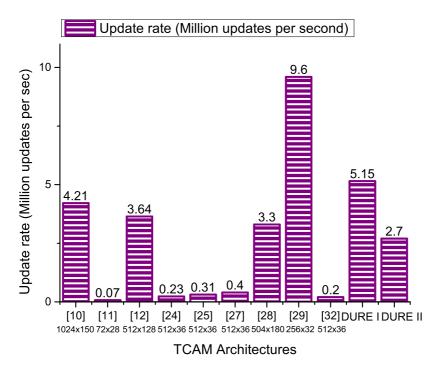

|         | 3.    | Update Rate                                          | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2      | 4.    | FPGA Resource Utilization | 66 |

|--------|-------|---------------------------|----|

| 4      | 5.    | Performance per Area      | 69 |

| 6      | 6.    | Energy-Delay Product      | 74 |

| V. CON | CLUSI | ONS & FUTURE WORK         | 79 |

| REFERE | NCES  |                           | 89 |

| ACKNOV | VLED  | GEMENTS                   | 90 |

## LIST OF ABBREVIATIONS AND ACRONYMS

| ASIC                              | Application-specific integrated circuit                                                                                               |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| CAM                               | Content-addressable memory                                                                                                            |

| BCAM                              | Binary Content-addressable memory                                                                                                     |

| TCAM                              | Ternary content-addressable memory                                                                                                    |

| SRAM                              | Static-random access memory                                                                                                           |

| FPGA                              | Field-programmable gate array                                                                                                         |

| BRAM                              | Block RAM                                                                                                                             |

| SL                                | Search line                                                                                                                           |

| MA                                | Match Address                                                                                                                         |

| ML                                | Match line                                                                                                                            |

| MLSA                              | Match line sense amplifier                                                                                                            |

|                                   | 1                                                                                                                                     |

| PE                                | Priority encoder                                                                                                                      |

| PE<br>LUT                         | -                                                                                                                                     |

|                                   | Priority encoder                                                                                                                      |

| LUT                               | Priority encoder<br>Look-up table                                                                                                     |

| LUT<br>LUTRAM                     | Priority encoder<br>Look-up table<br>Look-up table RAM                                                                                |

| LUT<br>LUTRAM<br>CLB              | Priority encoder<br>Look-up table<br>Look-up table RAM<br>Configurable logic block                                                    |

| LUT<br>LUTRAM<br>CLB<br>SR        | Priority encoder<br>Look-up table<br>Look-up table RAM<br>Configurable logic block<br>Slice register                                  |

| LUT<br>LUTRAM<br>CLB<br>SR<br>TLB | Priority encoder<br>Look-up table<br>Look-up table RAM<br>Configurable logic block<br>Slice register<br>Translation look-aside buffer |

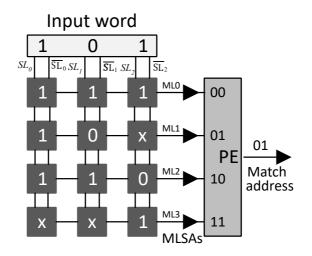

| 1 | A 4 $\times$ 3 TCAM: (MLSAs: Match line sense amplifiers)                   | 2  |

|---|-----------------------------------------------------------------------------|----|

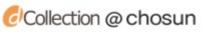

| 2 | SRAM-based implementation of a 4 $\times$ 3 TCAM: (PE: priority             |    |

|   | encoder, and MA: match address)                                             | 3  |

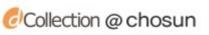

| 3 | Multipumping-based multiported memory: the SRAM block is                    |    |

|   | clocked at an integral multiple of $P$ , allowing $P$ access during         |    |

|   | one external clock cycle                                                    | 13 |

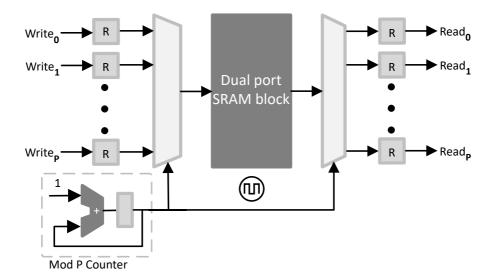

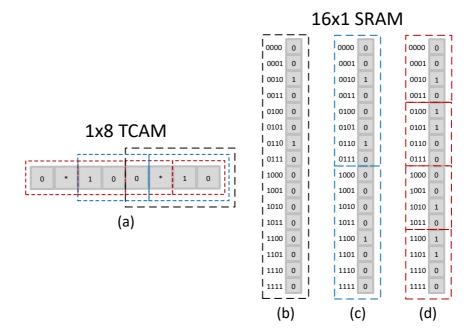

| 4 | (a) A conventional TCAM of $1 \times 8$ ; (b) An $16 \times 1$ SRAM without |    |

|   | multipumping emulating $1 \times 4$ TCAM; (c) An $16 \times 1$ SRAM with    |    |

|   | a multipumping factor of $P = 2$ emulating $1 \times 6$ TCAM; (d) An        |    |

|   | $16 \times 1$ SRAM with a multipumping factor of $P = 4$ emulating          |    |

|   | $1 \times 8$ TCAM                                                           | 14 |

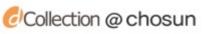

| 5 | Proposed partitioning of the traditional TCAM table                         | 16 |

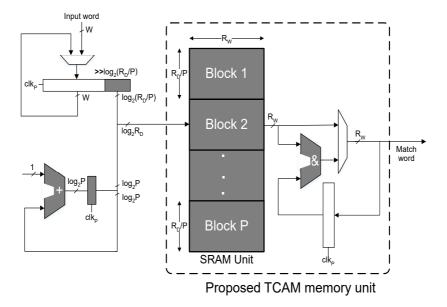

| 6 | Basic architecture of the proposed TCAM memory                              | 17 |

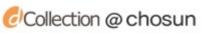

| 7 | Organization of the proposed TCAM memory units for a large                  |    |

|   | storage capacity: (IW: input word, PE: priority encoder, OPE:               |    |

|   | overall priority encoder)                                                   | 18 |

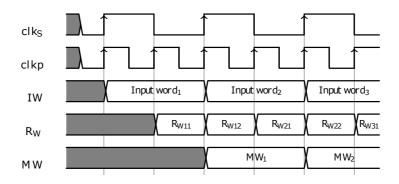

| 8 | Timing diagram for the search operation in our proposed TCAM                |    |

|   | with a multipumping factor $P = 2$ : ( <i>IW</i> : input word, $R_W$ : SRAM |    |

|   | word read, $MW$ : match word)                                               | 19 |

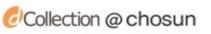

| 9 | Example of the proposed classification algorithm: $(a)$ Description         |    |

|   | of Classification based on set of bit positions $S_1 = \{b_0, b_1\}$ .      |    |

|   | (b) Description of Classification based on set of bit positions             |    |

|   | $S_2 = \{b_1, b_3\}$ .                                                      | 29 |

조선대학교 CHOSUN UNIVERSITY

| 10 | Example of mapping proposed classification scheme constructed                                                  |    |

|----|----------------------------------------------------------------------------------------------------------------|----|

|    | TCAM-subtables to SRAM: (a) Mapping TCAM sub-tables                                                            |    |

|    | contents to SRAM constructed based on set of bit positions                                                     |    |

|    | $S_1 = \{b_0, b_1\}$ . (b) Mapping TCAM sub-tables contents to SRAM                                            |    |

|    | constructed based on set of bit positions $S_2 = \{b_1, b_3\}$                                                 | 31 |

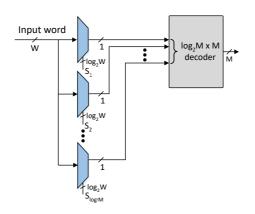

| 11 | Architecture of the pre-classifier unit: (S: Select lines for                                                  |    |

|    | extracting the pre-classification bits, $log_2W$ : Number of bits in                                           |    |

|    | the , $log_2M$ : Number of pre-classifier bits, $M$ : Number of enable                                         |    |

|    | control bits for the <i>M</i> rows of SRAM blocks)                                                             | 35 |

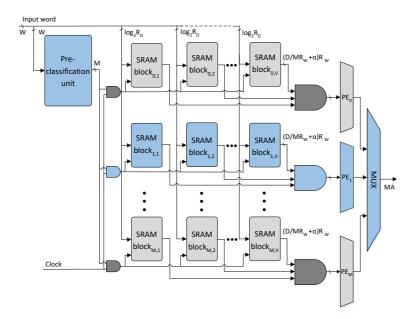

| 12 | Proposed overall architecture: (M: Number of rows of SRAM                                                      |    |

|    | blocks, V: Number of SRAM blocks in a row, PE: priority                                                        |    |

|    | encoder unit, MA: matching address, $log_2R_D$ : Address bits of the                                           |    |

|    | configured SRAM blocks, $\left(\left\lfloor \frac{D}{MR_W} \right\rfloor + \alpha\right)R_W$ : Configured SRAM |    |

|    | blocks words width).                                                                                           | 35 |

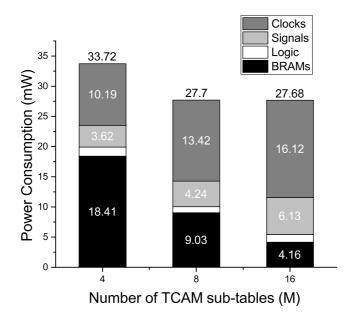

| 13 | Trade-Off between the Number of TCAM Sub-Tables (M) and                                                        |    |

|    | Power Consumption Performance                                                                                  | 42 |

| 14 | A simplified implementation of DURE.                                                                           | 50 |

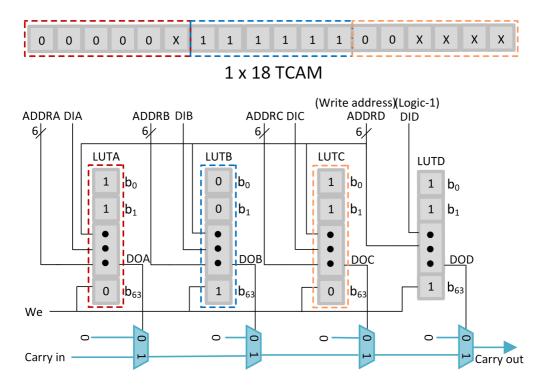

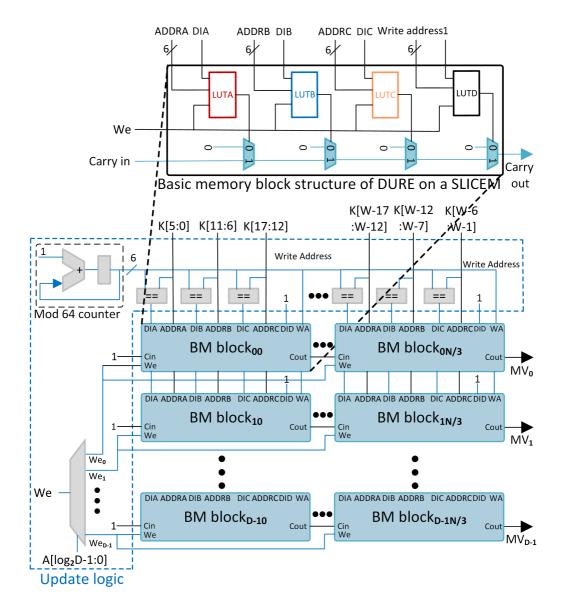

| 15 | Architecture of the basic memory block of DURE for                                                             |    |

|    | implementing an $1 \times 18$ TCAM on FPGA                                                                     | 51 |

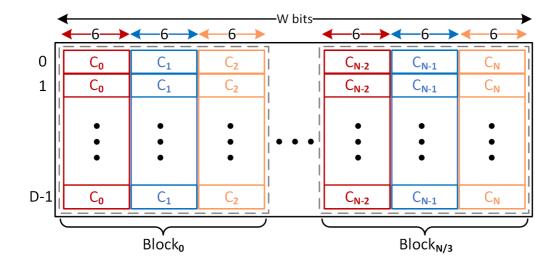

| 16 | Partitioning TCAM table contents into 6-bit chunks                                                             | 52 |

| 17 | Architecture of the proposed DURE                                                                              | 53 |

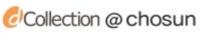

| 18 | LUTRAM utilization trend for increasing TCAM depth (D) and                                                     |    |

|    | width (W)                                                                                                      | 59 |

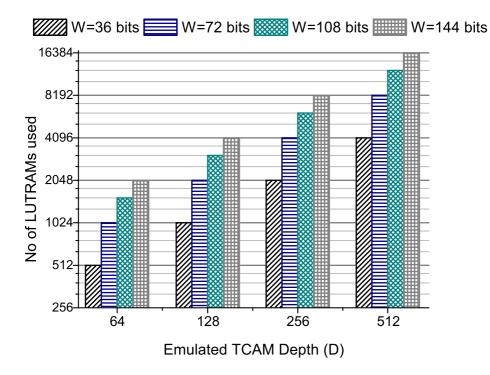

| 19 | Slice registers usage trend for increasing TCAM depth (D) and                                                  |    |

|    | width (W)                                                                                                      | 60 |

| 20 | Clock rate trend for increasing TCAM depth (D) and width (W).                                                  | 61 |

| 21 | Power consumption trend for increasing TCAM depth (D) and      |    |

|----|----------------------------------------------------------------|----|

|    | width (W)                                                      | 62 |

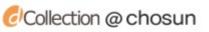

| 22 | Update rate trend for increasing TCAM depth (D) and width (W). | 63 |

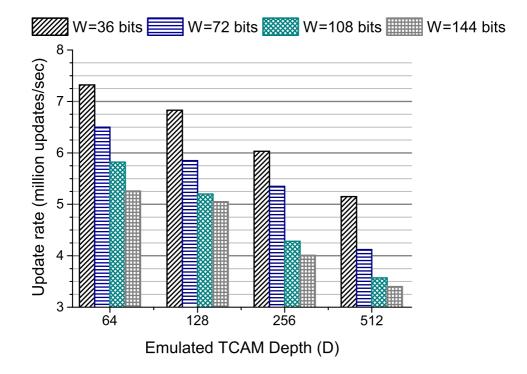

| 23 | Search latency comparison                                      | 64 |

| 24 | Update rate comparison.                                        | 65 |

## LIST OF TABLES

| 1  | List of basic notations used                                                | 11 |

|----|-----------------------------------------------------------------------------|----|

| 2  | FPGA resource utilization of the proposed design                            | 21 |

| 3  | Performance per memory comparison of the proposed TCAM                      |    |

|    | with previous approaches                                                    | 26 |

| 4  | A TCAM table of size $6 \times 6$                                           | 29 |

| 5  | FPGA resource utilization of EE-TCAM on Xilinx Virtex-6                     | 38 |

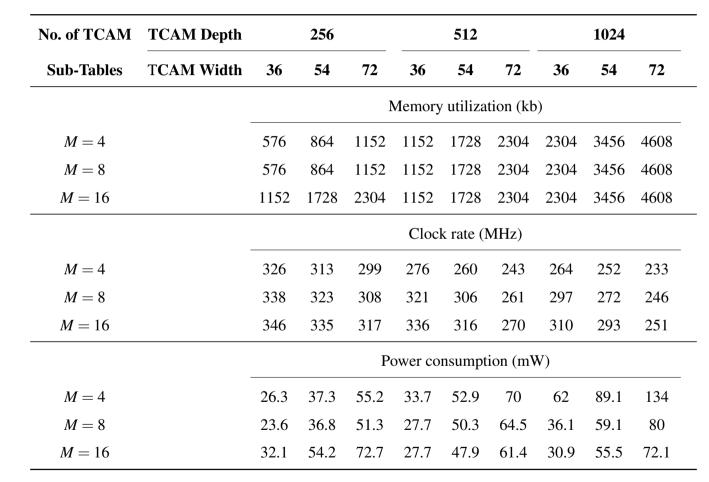

| 6  | Performance trend for increasing EE-TCAM depth (D), width                   |    |

|    | (W) in various configurations. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 40 |

| 7  | Comparison of the power consumption per performance with                    |    |

|    | previous works.                                                             | 46 |

| 8  | A $3 \times 4$ TCAM table                                                   | 49 |

| 9  | FPGA resource utilization for proposed DURE                                 | 58 |

| 10 | FPGA resource utilization for implementing various TCAM                     |    |

|    | architectures                                                               | 68 |

| 11 | Performance per area comparison with existing FPGA-based                    |    |

|    | TCAM architectures                                                          | 72 |

| 12 | Energy-delay product (EDP) comparison for various FPGA-                     |    |

|    | based TCAM solutions                                                        | 76 |

### ABSTRACT

### High-Performance Ternary Content Addressable Memory Architecture for FPGAs

Inayat Ullah

Advisor: Prof. Lee, Jeong-A, Ph.D. Department of Computer Engineering Graduate School of Chosun University

Ternary content-addressable memory (TCAM) is widely employed to design high-speed search engines and has applications in networking, artificial intelligence, and to accelerate various database search primitives. TCAMs are built either as application-specific integrated circuits (ASIC) natively or static random-access memory (SRAM)-based field-programmable gate arrays (FPGAs) are used to emulate TCAM by addressing the SRAM with TCAM contents. The search space demands of TCAM applications are constantly rising. However, existing realizations of TCAM on FPGAs suffer from storage inefficiency. Native TCAMs and SRAM-based TCAMs both have a high power consumption drawback. The SRAM-based TCAMs offer promising lookup performance, however, the update process in a TCAM table poses significant challenges to their efficient employment. SRAM-based TCAMs for FPGAs, suspend search operations during an already high-latency update operation rendering them infeasible in applications that require high-frequency updates. This thesis presents three approaches to overcome the aforementioned limitations in existing

FPGA-based TCAMs i.e. storage inefficiency, higher power consumption, and high-latency blocking updates.

We first propose a multipumping-enabled multiported SRAM-based TCAM design on FPGAs to achieve efficient SRAM utilization. Existing SRAM-based TCAM solutions reduce the impact of the increase in the traditional TCAM pattern width from an exponential growth in memory usage to a linear one with the use of cascaded block RAMs (BRAMs) on FPGA. However, BRAMs on state-of-the-art FPGAs have a minimum depth limitation, which limits the storage efficiency for TCAM bits. Our proposed solution avoids this limitation by mapping the traditional TCAM table divisions to shallow sub-blocks of the BRAMs towards memory-efficient TCAM design. Using the multipumping technique, the proposed solution operates the simple dual-port BRAMs of the design as multiported SRAM by clocking them with a higher internal clock frequency to access the sub-blocks of the BRAM in a single system cycle. We implemented the proposed design on a Virtex-6 FPGA device and compared with the existing FPGA-based TCAM designs, our proposed method achieves up to 2.85 times better performance per memory.

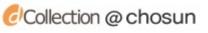

A pre-classifier-based architecture for a low-power SRAM-based TCAM is also presented. The first classification stage divides the TCAM table into several sub-tables of balanced size. The second SRAM-based implementation stage maps each of the resultant TCAM sub-tables to a separate row of SRAM blocks in the architecture. The proposed design selectively activates at most one row of SRAM blocks for each incoming TCAM word. Compared with the existing SRAMbased TCAM designs on FPGAs, the proposed design consumes significantly lower energy as it activates only a part of SRAM memory being used for lookup rather than the entire SRAM memory. We implemented the proposed approach on

a Xilinx Virtex-6 FPGA and our experimental results showed that the proposed design achieved at least three times lower power consumption per performance than other SRAM-based TCAM architectures.

A dynamically updateable energy- and resource-efficient TCAM design (DURE) based on FPGAs is also presented in this thesis. DURE exploits the distributed RAM resources in FPGAs, more specifically, the look-up table RAMs (LUTRAMs) available in SLICEM resources are configured as quad-port RAM, which constitutes the basic memory (BM) block in the implementation of DURE. The contents of the TCAM table are divided into chunks of equal size and are mapped onto the LUTRAMs of the proposed BM blocks. DURE implements dynamic updates by reconfiguring the LUTRAMs of only those BM blocks that are associated with the word being updated, thereby allowing search and update operations to be performed simultaneously. Compared with existing SRAM-based TCAMs, DURE has a smaller single cycle search latency and achieves at least 2.5 times more energy-delay product efficiency and a 67% higher performance per area.

In this thesis, we have presented three high-performance TCAM architectures which achieve higher memory efficiency, better energy-delay product efficiency, and implement dynamic updates. Our proposed solutions are general and can be adapted in many applications. In the future, we will explore the adoption of these designs in various applications for further evaluation.

## 한글요약

FPGA 기반 고성능 TCAM 구조

인야앳울라 지도 교수: 이정아 컴퓨터공학과 대학원, 조선대학교

TCAM (Ternary Content-Addressable Memory)은 고속 검색을 필요로 하는 네 트워킹, 인공지능 등 다양한 분야에서 핵심엔진으로 이용된다. TCAM은 주문 형 반도체(ASIC)로 바로 구현될 수 있으나 전력소모가 많은 단점이 있었으며, TCAM 내용을 SRAM의 주소로 이용하여 FPGA로 구현될 수 있었으나, 대용량 검색의 요구가 늘어감에 따라, 전력소모 증가와 스토리지 비효율성이란 문제 가 있었다. 그리고 SRAM 기반으로 설계된 TCAM은 빠른 검색을 가능하게 하 나, TCAM 테이블의 업데이트가 필요한 경우, 검색이 중단되는 문제점이 있었 으며, 잦은 업데이트가 발생하는 응용에서는 활용이 어려웠다. 본 논문에서는 기존의 FPGA기반 TCAM 구조의 문제점인 스토리지 비효율, 높은 전력소비, 그리고 업데이트 발생 시 검색 중단으로 인한 대기시간 증가를 극복하기 위한 세 가지 해결방안을 제시한다.

첫 번째로 SRAM 기반 TCAM 구조에서 SRAM 메모리의 효율적인 활용 을 위하여, 멀티펌핑 가능한 멀티포트 TCAM 구조를 제시한다. TCAM 검색 워드 크기가 증가함에 따라 필요한 SRAM 메모리가 폭발적으로 증가하는 문 제를 해결하기 위한, 기존의 해결책은 FPGA의 연결식 블록 RAM(BRAM)을 사용하는 것이었다. 그러나 최첨단 FPGA의 BRAM은 최소깊이 제한이 있어 TCAM 비트의 저장 효율성을 제한한다. 본 논문에서는 이러한 한계를 피하기

xii

위하여, 기존의 TCAM 테이블영역을 구성된 BRAM의 얕은 하위블록에 매핑 하여 메모리 효율적인 TCAM 메모리설계를 구현한다. 제안된 솔루션은 단일 시스템 사이클에서 BRAM의 하위블록에 액세스하기 위해 보다 높은 내부 클 록주파수로 클러킹 함으로써 다중펌핑 기술을 사용하여 멀티포트 SRAM으로 구성된 BRAM을 작동시킨다. 제안된 디자인을 Xilinx Virtex-6 FPGA에 구현 하여, 기존의 FPGA 기반 TCAM 설계와 비교하여 제안 된 방법이 메모리 당 최대 2.85 배의 성능을 달성함을 보였다.

그리고 SRAM 기반 TCAM 구조의 높은 전력소모를 해결하는 방안으로, 사전 분류기 기반 TCAM 구조를 제시한다. 첫 번째 분류를 통하여 TCAM 테 이블을 균형 잡힌 크기의 몇 개의 서브-테이블로 분할한다. 이렇게 분할된 서 브-테이블을 SRAM 블록의 분리된 개별 행에 매핑하여 구현한다. 본 구조는 TCAM 워드 검색시 전체가 아닌 일부에 해당하는 하나의 SRAM 블록 행만을 선택적으로 활성화하기 때문에 기존의 SRAM 기반 TCAM 구조와 비교할 때 에너지 소비를 크게 줄인다. 제안된 구조를 Xilinx Virtex-6 FPGA에 구현하여 기존의 SRAM 기반 TCAM 구조에 비하여 성능 당 적어도 3 배 이상 낮은 전력 소비를 달성함을 보였다.

세 번째로 검색을 하면서 동적 업데이트가 가능한 에너지 및 자원 효율적 인 DURE TCAM 구조를 제시한다. DURE 구조에서는 FPGA의 분산 RAM인 SLICEM 리소스의 룩업테이블 RAM (LUTRAM)을 활용하여, 쿼드포트 RAM 으로 구현된 LUTRAM들을 기본 메모리(BM) 블록으로 이용한다. TCAM 테 이블의 내용은 동일한 크기로 분할 되어 제안 된 BM 블록에 있는 LUTRAM 에매핑된다. DURE는 업데이트 되는 워드와 연관된 BM 블록의 LUTRAM만 을 재구성하여 동적 업데이트를 구현하므로 검색 및 업데이트 작업을 동시에 수행할 수 있다. 기존의 SRAM 기반 TCAM 구조와 비교할 때, DURE는 검색소 요시간이 짧으며 에너지와 수행시간를 모두 고려한 효율이 기존에 비하여 2.5 배 이상 향상 되고, 면적 당 67% 더 높은 성능을 달성한다.

xiii

본 논문에서는 FPGA 기반 고성능 TCAM 구조를 다양하게 제시하여, 메 모리 효율을 높이고, 에너지와 수행시간을 모두 고려한 효율을 향상시켰으며, 동적 업데이트를 가능하게 하였다. 본 논문에서 제안 된 구조는 범용적인 것으 로 다양한 어플리케이션에 적용이 가능하며, 이와 관련된 연구를 추후 진행할 예정이다.

## I. INTRODUCTION

#### A. Background

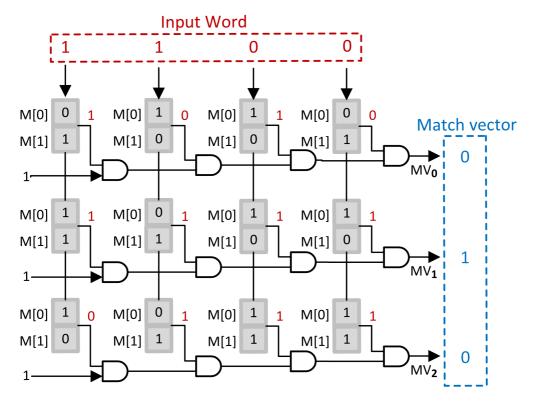

Content addressable memory (CAM) selects a word among stored data based on its contents. CAM compares an input word with its entire stored data in parallel and outputs the matched word's address in a single cycle. CAM is mainly categorized into two: Binary CAM (BCAM) that store only two states, "0" and "1", and ternary CAM (TCAM) that also store and compare an additional third state, known as the "don't care state x". The don't care state "x" is used to store wild card entries in TCAM words.

TCAMs designed as a dedicated system in the application-specific integrated circuit (ASIC) are known as traditional TCAMs. It compares the search key with the entire stored TCAM words in parallel and outputs the address of the matching word in one cycle. The circuitry of a TCAM cell store and compare three states: "0", "1", and don't-care state "x". TCAM architecture is composed of an array of TCAM cells and a priority encoder (PE). Each TCAM cell comprises two SRAM cells storing a ternary bit and an associated comparison circuitry. Search lines (SLs) provide search key bits to the corresponding cells of the TCAM words. The comparison results of each TCAM word are placed on the match lines (MLs). In case the matching of the search key is successful with more than one TCAM word, the PE selects the matching address with the highest priority. Figure 1 shows a sample design of  $4 \times 3$  traditional TCAM. For example, an input word of 101 is applied to the search lines of a  $4 \times 3$ traditional TCAM shown in Figure 1. The TCAM words of Row 1 and 3 are found to match completely and the corresponding match lines ML1 and ML3 remain high. The PE selects the address of ML1 as the match address based on

Figure 1: A  $4 \times 3$  TCAM: (MLSAs: Match line sense amplifiers).

priority. CAM is widely employed to design perform high-speed search engines for a variety of emerging applications, in the areas of networking as look-up table [1, 2, 3, 4], in microprocessors as translation-look-aside buffer (TLB) cache [5, 6, 7, 8], in big-data analytics as database accelerators [9, 10, 6], and in image processing, pattern recognition, and DNA sequence matching as Local binary patterns recognition system [11, 12, 13, 14, 6]. The Internet-of-things and bigdata processing devices employ TCAM as a filter when storing signature patterns, and achieve a substantial reduction in energy consumption by reducing wireless data transmissions of invalid data to cloud servers [9, 15].

Static random-access memory (SRAM)-based implementations of TCAM consist of an SRAM memory and a PE as shown in Figure 2. All the data of the original TCAM is mapped to the SRAM memory. For a TCAM table of size  $A \times B$  (*A* words of *B* bits width), the SRAM-based implementation requires  $2^B$  words of *A* bits width. Figure 2 shows the SRAM-based implementation of a  $4 \times 3$  TCAM. It comprises of a  $2^3$  SRAM words of 4-bits each. The SRAM words

Figure 2: SRAM-based implementation of a 4  $\times$  3 TCAM: (PE: priority encoder, and MA: match address)

store the match/ mismatch information on comparison with the TCAM words of all locations of the original TCAM for all possible combinations of input words. Bit positions 0, 1, 2, and 3 of the 1st SRAM word stores the match/mismatch information of the input word 000 with TCAM words of all four locations 0, 1, 2, and 3 respectively. Likewise, the SRAM words 0, 1, 2, ..., 7 store the match/mismatch information of all eight possible input words with TCAM words of all four locations at bit positions 0, 1, 2, and 3. The input word 101 matches successfully with TCAM words at locations 1 and 3. Accordingly, the SRAM memory for the  $4 \times 3$  TCAM implementation stores high bits at bit positions 1 and 3 of the input word's 101 addressed location.

#### **B.** Problem Statement

Field-programmable gate arrays (FPGAs) emulate TCAM using SRAM, by addressing SRAM with TCAM contents. Each SRAM word corresponds to a

specific TCAM pattern, and stores information on its existence for all possible data of the TCAM table. The increase in the number of TCAM pattern bits results in an exponential growth in memory usage. This exponential growth in memory usage has been reduced to linear growth by cascading multiple SRAM blocks in the design of TCAM on FPGA in previous work [16, 17].

Contemporary FPGAs implement block-RAM (BRAM) in the silicon substrate and offer a high speed. For example, Xilinx Virtex-6 xc6v1x760 FPGA contains 720 BRAMs of size 36 Kb [18], and provide operating frequencies of greater than 500 MHz [19]. Designers utilize these high-speed SRAM blocks to design SRAM-based TCAMs on FPGA. In existing SRAM-based solutions, the storage capacity of a BRAM for TCAM bits is limited by its higher SRAM/TCAM ratio  $\frac{2^9}{9}$ , because of its minimum depth limitation of  $512 \times 72$  when configured in simple dual-port mode on FPGA [18]. For example, the design methodologies proposed in [20], [21], and [22], require a total of 56, 40, and 40 BRAMs of size 36 Kb, respectively, to implement an 18 Kb TCAM.

Excessive usage of BRAMs in the design of TCAM can result in a lack of BRAMs for other parts of the system on FPGA. Furthermore, the limited amount of BRAM resources on FPGA can compel designers to implement TCAMs in distributed RAM using SLICEM, resulting in the consumption of many slices, and a limitation on the maximum clock frequency of the design. This problem becomes more severe for the design of large storage capacity TCAMs. The efficient utilization of SRAM memory is imperative for the design of TCAMs on FPGAs.

Existing SRAM-based TCAMs on FPGAs suffer from higher energy consumption as they consume excessive power to energize the entire SRAM memory used per lookup. For example, the SRAM-based TCAM design

methodologies presented in recent works [23, 24] consumed 2.5 W and 3.2 W to implement 89 kb and 150 kb TCAM tables using BRAMs on FPGA, respectively. The higher power consumption of SRAM-based TCAM designs becomes more severe for larger capacities.

A single update in SRAM-based TCAM requires rewriting all of the SRAM blocks configured by the design, owing to TCAM's support for wild card entries. The update process for a TCAM word in an SRAM-based TCAM architecture includes writing the update word and erasing the old TCAM word from SRAM blocks. This process involves the indexing of all the words of an SRAM block for writing. Such TCAMs implement dedicated update engines for writing the SRAM blocks in parallel, which introduces an excessive additional hardware overhead. Hence, the minimum number of cycles required for an update process is proportionate to the depth of the utilized SRAM blocks [17, 25].

In addition, during the update process in SRAM-based TCAM search operations remain suspended. Therefore, such TCAMs dedicate a substantial amount of clock cycles to supporting high-latency blocking updates in frequent update environments, thereby substantially lowering the arrival rate of input words for lookup [26]. Because lookup operations are locked during high latency updates, SRAM-based TCAMs require a large buffer space to store input words, in order to avoid the loss of these words [27, 28]. As such, despite the search performance of one search per cycle, these TCAMs are infeasible for use in high-churn-rate environments, where frequent TCAM updates are required. This critical TCAM table update issue in SRAM-based TCAM architectures has not so far been addressed. Therefore, further research on implementing dynamic updates in the FPGA-based TCAM architectures is required.

A TLB cache is an integral part of any processor architecture and is

implemented using CAM [29, 5, 7]. Soft-core processors implemented in reconfigurable hardware such as FPGAs are widely employed in embedded system applications [30]. A low response time (single cycle) dynamically updateable CAM architecture is required in the design of a non-blocking TLB cache for soft-core processors [31, 32, 33]. However, existing RAM-based TCAM architectures on FPGAs suffer from high search latencies (high response times) and update operations during which searches are suspended.

#### C. Motivations

The significant advancement in CMOS technology has made modern FPGAs an attractive choice for implementing emerging systems because of their offered massive parallelism with flexibility through on-the-fly reconfiguration. Contemporary SRAM-based FPGA device such as the 40-nm Xilinx Virtex-6 FPGA consists of a large amount of embedded memory that operates at high speed with low power consumption.

The demand for a high-speed flexible (re-configurable) and adaptable (easy for integration) TCAM configurations renders the embedded memories (BRAMs and distributed RAM) on modern SRAM-based FPGAs attractive for the design of TCAMs. Configurable CAM architectures are desirable in embedded hardware, in order to be able to adapt to the requirements of the intended application to strike an optimal balance between the area, power, and speed [34, 35, 4].

#### **D.** Thesis Contributions

This thesis proposed three different approaches for designing memory-efficient, energy-efficient and dynamically updateable TCAM architectures for FPGAs.

The contributions of this thesis are summarized as follows:

- A novel multipumping-enabled multiported SRAMbased TCAM architecture, which achieves efficient memory utilization, is proposed. Compared to existing FPGA-based TCAM architectures, Our proposed design achieves a performance that is up to 2.85 times higher performance per memory.

- A pre-classifier-based architecture for SRAM-based TCAM design is proposed, which achieves a considerable reduction in energy consumption. Compared to prior work, our architecture exhibits at least 3 times lower power consumption per performance

- A dynamically updatable FPGA-based TCAM architecture using LUTRAM FPGA primitives is proposed. The proposed architecture targets TCAM applications where high-frequency updates are required. The main challenge in the efficient use of FPGA-based TCAM is the high latency blocking update operation, which is resolved by the proposed solution.

- The proposed dynamically updatable FPGA-based TCAM architecture is both energy and resource efficient. Compared with the existing state-ofthe-art TCAM solutions, it achieves up to 67% more performance per area and at least 2.5 times better energy-delay product efficiency.

#### E. Related Work

Existing FPGA-based TCAM architectures are mostly RAM-based solutions employing block-RAM (BRAM) or distributed RAM resources for implementing TCAM. The BRAM-based TCAM solutions presented in previous work [20, 21, 22] store the knowledge about the presence of TCAM words and their address information in separate sets of BRAM units and thus suffer from inefficient memory usage. These works suffer from higher power consumption as the entire used excessive SRAM memory is activated for the incoming TCAM word lookup. The update process for such TCAMs includes updating a copy of the TCAM table, which is then remapped to the BRAM configured by the design on the FPGA. As such, all the BRAMs configured by the TCAM are rewritten, which is time-consuming and expensive in terms of the additional logic overhead.

The BRAM-based TCAM solutions presented in [16, 17, 25, 26, 36, 37] store the knowledge about the presence of the TCAM word and their address information in the same BRAM block. These approaches suffer from reduced memory efficiency because of the limited storage capacity of BRAM for storing the TCAM bits, owing to a higher SRAM/TCAM ratio of  $2^9/9$  [17]. However, these works [16, 17, 25, 26, 36, 37] energize all used SRAM memory blocks in the design for each incoming TCAM word's lookup, and thus, consumes higher power consumption. The update process in the SRAM-based TCAMs from [16, 17, 20, 21, 22, 26, 36, 37] requires dedicated update engines to write all of the SRAM blocks used by the design in parallel, which results in an additional logic overhead. In this manner, the write cycle in the update process becomes proportional to the depth of the design-configured BRAMs, which requires 513 clock cycles [17, 25].

The distributed RAM-based TCAM solutions presented in previous work [17, 26, 36] achieve a higher memory efficiency, because of increased storage capacity for TCAM bits in distributed RAM with an SRAM/TCAM ratio of  $2^5/5$ . However, when implementing a large TCAM table, the bitwise-ANDing of a large number of wide bit vectors becomes time-critical, resulting in a reduced achievable throughput. Although these designs have a relatively small update latency of 33 cycles, they suffer from an expensive rewriting of the entire configured SRAM memory, on account of supporting wild card entries.

Xilinx has presented several implementation techniques for binary CAM using BRAM and for TCAM using the shift register (SRLE16) on FPGAs in its application note [37]. The BRAM-based binary CAM technique is storage-inefficient. The TCAM implementation technique, which employs LUT resources as shift registers, has reduced resource efficiency, as only two TCAM bits are encoded and are mapped on a single 16-bit shift register LUT primitive SRLE16. For larger TCAM table implementations, this technique suffers from timing problems arising because of routing congestion.

A fast content updating mechanism for SRAM-based TCAM is presented in [38]. Its update latency depends on the number of "don't care" bits in the subwords of an update word. However, this TCAM approach, which is implemented using Xilinx BRAM resources, has the worst case update latency, being 513 cycles.

The multiplexer-based TCAM design presented in the patent [39] suffers from a degraded system throughput owing to the sequential searching of the TCAM data for the input word, i.e., a single TCAM word is searched per cycle. This technique stores the contents of the TCAM table in the LUTRAMs from the SLICEM resources, while the comparison circuitry is implemented using

programmable FPGA interconnects. The outputs of the comparison circuits are further *AND* cascaded to implement multiple bits of the TCAM word.

RAM-based associative CAM was presented in a U.S. patent [40]. Its memory requirement increases exponentially with the increase in the pattern bits of CAM. For large bit patterns, it does not scale well in terms of the memory requirement, power consumption, and cost. Thus, it is not feasible to implement it on ASIC or FPGA platforms.

A set-associative memory architecture implemented in hardware using the well-known hashing method was presented in [41]. It used RAM memory to implement CAM. However, in order to support TCAM functionality, the architecture suffered from inefficient memory utilization as it required two bits to encode ternary bits.

In contrast to the existing SRAM-based TCAMs, our proposed multipumping-enabled multiported SRAM-based TCAM design exploits the efficient utilization of SRAM memory by mapping TCAM divisions to shallow sub-blocks of BRAMs on FPGA. It operates high-speed BRAMs in the design as multipumping-enabled multiported SRAM, maintaining a high system throughput.

In this thesis, we present a pre-classifier-based architecture for an energyefficient SRAM-based TCAM design (EE-TCAM). We first classify a TCAM table into several TCAM sub-tables, which are further partitioned vertically. Each partitioned TCAM sub-table is implemented as a row of cascaded SRAM blocks in the proposed architecture. For each input TCAM word, at most one row of SRAM blocks is activated in the proposed design, significantly reducing the dynamic power consumption compared with the existing SRAM-based TCAMs.

In contrast to previous related SRAM-based TCAM designs, this thesis

presents a dynamically updateable energy- and resource-efficient TCAM design (DURE). DURE maps the contents of a TCAM table onto the LUTRAMs available in SLICEM resources, which together with the available fast carry chains implements the desired TCAM functionality, achieving a single cycle search latency. DURE dynamically reconfigures only the LUTRAMs associated with the word being updated, without suspending search operations.

| Notations    | Description                              |

|--------------|------------------------------------------|

| D            | Depth of traditional TCAM                |

| W            | Width of traditional TCAM                |

| $R_D$        | Depth of the configured SRAM blocks      |

| $R_W$        | Width of the configured SRAM blocks      |

| $log_2(R_D)$ | Address bits of the SRAM block           |

| Р            | Number of sub-blocks in an SRAM block /  |

| P            | Multipumping factor                      |

| $R_D/P$      | Depth of the sub-blocks in an SRAM block |

| М            | Rows of the TCAM divisions /             |

| M            | Rows of the TCAM memory units            |

| N            | Columns of the TCAM divisions /          |

| 1            | Columns of the TCAM memory units         |

Table 1: List of basic notations used.

#### F. Thesis Organization

This thesis is organized as follows. Chapter II describes multipumping-enabled multiported SRAM-based TCAM architecture, its FPGA implementation results

and comparison with existing FPGA-based TCAM architectures. Chapter III details the pre-classification based energy efficient TCAM architecture and evaluates its performance based on its comparison with other existing TCAM solutions on FPGAs. Chapter IV explains the dynamically re-configurable LUTRAM-based energy- and resource- efficient TCAM architecture and its performance evaluation is detailed. Finally, Chapter V concludes this work. Table 1 lists the description of the basic notations used in the thesis.

## II. MULTIPUMPING ENABLED MULTIPORTED SRAM-BASED TCAM ARCHITECTURE

#### A. Multipumping-Enabled Multiported SRAM

The multipumping technique multiplies the ports of a dual ported SRAM block by internally clocking it at an integral multiple of the external system clock [42, 43, 44, 45]. The addresses and data are registered and provided access to the SRAM block in a circular order by using mod P counter bits as shown in Figure 3. Several designs utilize multipumping for the implementation of efficient multiported memory [46, 47].

Figure 3: Multipumping-based multiported memory: the SRAM block is clocked at an integral multiple of *P*, allowing *P* access during one external clock cycle.

Figure 4: (a) A conventional TCAM of  $1 \times 8$ ; (b) An  $16 \times 1$  SRAM without multipumping emulating  $1 \times 4$  TCAM; (c) An  $16 \times 1$  SRAM with a multipumping factor of P = 2 emulating  $1 \times 6$  TCAM; (d) An  $16 \times 1$  SRAM with a multipumping factor of P = 4 emulating  $1 \times 8$  TCAM.

#### 1. Basic Idea

In the SRAM-based implementation of TCAM, the depth of the traditional TCAM determines the width of SRAM memory, and the width of the traditional TCAM is encoded as the address of the SRAM memory. The basic concept of the proposed multipumped SRAM-based TCAM implementation achieving increased memory efficiency is shown in Figure 4. Figure 4(a) shows a  $1 \times 8$  traditional TCAM table, and Figure 4(b) shows the implementation of the four TCAM bits (0\*10) by using a  $16 \times 1$  SRAM block. Figure 4(c) shows the implementation of six TCAM bits (100\*10) by using  $16 \times 1$  SRAM block, which

has been multipumped two times, each SRAM sub-block of size  $8 \times 1$  emulating three TCAM bits. Figure 4(d) shows the implementation of eight TCAM bits (0\*1000\*10) by using  $16 \times 1$  SRAM block, which has been multipumped four times, each SRAM sub-block of size  $4 \times 1$  emulating two TCAM bits. Thus, designing TCAM using multipumping-enabled multiported SRAM in Figure 4(c) and (d) achieved a higher SRAM memory efficiency (i.e. fewer SRAM bits are utilized per TCAM bit) when compared with that of multipumping-less SRAMbased TCAM design in Figure 4(b). The TCAM bits storage capacity of the SRAM block increases with multipumping.

A multiported SRAM block of size  $R_D \times R_W$  with a multipumping factor of P implements a traditional TCAM table of size  $Plog_2(R_D/P) \times R_W$ , each SRAM sub-block of size  $(R_D/P) \times R_W$  emulating  $log_2(R_D/P) \times R_W$  TCAM data, as shown in Figure 5 and 6. Our proposed design achieves increased TCAM bits storage capacity with an increase in multipumping factor P.

#### 2. Proposed Partitioning of Traditional TCAM Table

Figure 5: Proposed partitioning of the traditional TCAM table.

We partition the traditional TCAM table of size  $D \times W$  into  $M \times N$  partitions such that each partition consists of *P* parts of  $log_2(R_D/P) \times R_W$  size as shown in Figure 5. Our proposed TCAM design uses its configured SRAM blocks of  $R_D \times$  $R_W$  size as multiported SRAM, constituting *P* sub-blocks of size  $(R_D/P) \times R_W$ as shown in Figure 6.

Each sub-block of the SRAM stores  $log_2(R_D/P) \times R_W$  size divisions of the traditional TCAM. Consequently the *P* sub-blocks of the multiported SRAM memory in our proposed design stores a traditional TCAM division of size  $Plog_2(R_D/P) \times R_W$  as shown in the Figures 5 and 6. Similarly, the  $M \times N$  TCAM divisions of size  $Plog_2(R_D/P) \times R_W$  are mapped to the SRAM blocks of the  $M \times N$  TCAM memory units in the proposed design, as shown in Figures 5 and 7.

Figure 6: Basic architecture of the proposed TCAM memory.

#### 3. Basic Architecture of the Proposed TCAM Memory

The basic architecture of our proposed TCAM memory design is shown in Figure 6. It is operated by two fully synchronized clocks, a system clock  $clk_S$ and internal clock  $clk_P$ , such that  $clk_P$  is P times faster than  $clk_S$ . An incoming TCAM word is registered in a W-bit shift register using the system clock  $clk_S$ . The  $log_2P$ -bit counter generates a sequence of  $log_2P$ -bit numbers in P internal clock cycles. It is initialized to zero upon reset and it rolls over after every Pinternal clock cycles. The  $log_2P$ -bits from the counter are concatenated with the  $log_2(R_D/P)$  bits from the shift register to make the  $log_2R_D$ -bit address space of the SRAM. At the positive edge of the internal clock  $clk_P$ , the SRAM address is executed such that  $log_2P$ -bits from the counter constitute its most significant bits, and points to the start of the corresponding sub-block in SRAM and the lower

$log_2(R_D/P)$  bits from the shift register selects an SRAM word in the sub-block.

The read SRAM words are *AND*-accumulated for each cycle in an  $R_W$ -bit register using  $clk_P$ . Similarly, the look-up is completed for a *W*-bit input word by reading and *AND*-accumulating SRAM words from each sub-block of the SRAM in *P* internal clock cycles or one system cycle. Consequently, the *P AND*-accumulated SRAM words are produced as match word using  $clk_S$ . The timing diagram in Figure 8 elaborates the search operation of the proposed TCAM memory architecture shown in Figure 6 with a multipumping factor of P = 2.

Figure 7: Organization of the proposed TCAM memory units for a large storage capacity: (*IW*: input word, *PE*: priority encoder, *OPE*: overall priority encoder)

Figure 8: Timing diagram for the search operation in our proposed TCAM with a multipumping factor P = 2: (*IW*: input word,  $R_W$ : SRAM word read, *MW*: match word)

#### 4. Modular Architecture

TCAM design of large storage capacity is implemented as a cascade of  $M \times N$ proposed design TCAM memory units as shown in Figure 7. An incoming *W*-bit TCAM word is divided into *N* sub-words of  $Plog_2(R_D/P)$ -bits with the bit ranges shown in Figure 7. The resultant sub-words are stored in *N* shift registers of size  $Plog_2(R_D/P)$ -bits on  $clk_S$ . The  $log_2R_D$ -bit indexes from the *N* shift registers are provided to the corresponding *M* TCAM memory units of the *N* columns of the proposed design in parallel using  $clk_P$ , as shown in Figure 7. All TCAM memory units of the design operate in parallel using  $clk_P$ . The  $R_W$ -bit match words from each row of the TCAM memory units are bit-wise *ANDed* on  $clk_S$ , and the results are provided to the associated priority encoder (PE) units. The  $log_2D$ -bit match address and the match information from each PE unit are provided to the overall priority encoder unit, which eventually forwards a match address based on the priority. The proposed TCAM design registers an input word and produces a match word as output on  $clk_S$ .

The update of a TCAM word is performed in each TCAM memory unit of

the design in parallel. The worst-case update latency of the proposed design comprises  $R_D/P$  system cycles.

# 5. Effect of Multipumping SRAM on the Memory Usage and Throughput

Multipumping results in a useful reduction in SRAM memory usage for the design of TCAM on FPGA. The configured SRAM memory blocks in our proposed design with the multipumping factor of *P* implements traditional TCAM divisions of size  $Plog_2(R_D/P) \times R_W$  as shown in Figure 6. The TCAM bits storage capacity of SRAM blocks in the proposed design increases with an increase in *P*. The upper bound on the multipumping factor *P* is  $R_D/2$ , i.e.  $R_D/2$  sub-blocks in the SRAM and each sub-block consists of two SRAM words.

Multipumping divides the achievable internal clock frequency of the design by the multipumping factor, to obtain the operating frequency of the overall system [42, 43, 44, 48]. Although an increase in the multipumping factor Presults in a higher memory efficiency for the design of TCAM, only the use of small multipumping factors is practical in order to avoid a significant drop in the operating frequency of the overall system. Overall multipumping factor P controls a tradeoff between the SRAM memory efficiency and speed of the proposed design.

## **B.** Implementation Setup and Results

To verify our proposed design we implemented it on a Xilinx Virtex-6 FPGA device (xc6v1x760). The proposed design was implemented using the Xilinx ISE 14.7 design tool, and verified through behavioral and post-route simulations using

an ISim simulator.

We implemented our proposed design cases I and II on the Xilinx Virtex-6 FPGA device for  $512 \times 28$  (14 Kb) and  $512 \times 32$  (16 Kb) TCAM tables, with multipumping factors of P = 4 and P = 2, respectively. Our proposed design CASE-III implements a large TCAM table of size  $1024 \times 140$  (140 Kb), with a multipumping factor of P = 4. We have selected small multipumping factors of P = 4, 2, and 4, in our proposed design cases I, II, and III, to avoid lower operating frequencies of the overall system.

Table 2 lists the FPGA resource utilization slice registers (SRs), look-up tables, and BRAMs for the implementation of our proposed design cases I, II, and III. The post place & route results show that the proposed design cases I, II, and III could achieve internal clock frequencies of 475 MHz, 475 MHz, and 349 MHz and multipumping factors of P = 4, 2, and 4, giving the system clock frequencies of 119 MHz, 237 MHz, and 87 MHz, respectively.

| Proposed design           | TCAM size         | Slice     | LUTs | BRAMs   |  |

|---------------------------|-------------------|-----------|------|---------|--|

| r roposed design          | $(D \times W)$    | registers | LUIS | (36 Kb) |  |

| CASE-I (P = 4)            | 512×28            | 536       | 968  | 8       |  |

| CASE-II (P = 2)           | 512 × 32          | 1593      | 1515 | 16      |  |

| <b>CASE-III</b> $(P = 4)$ | $1024 \times 140$ | 6287      | 7516 | 80      |  |

Table 2: FPGA resource utilization of the proposed design.

## C. Performance Evaluation & Comparison

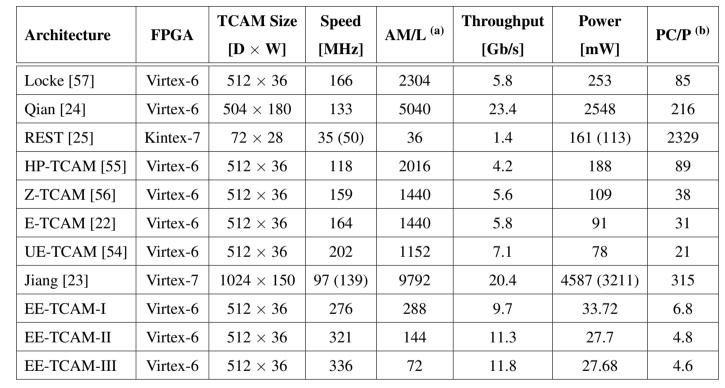

The performance of our proposed design is evaluated based on its comparison with the existing SRAM-based TCAM solutions on FPGAs.

#### 1. SRAM Memory Utilization

SRAM-based TCAM solutions implement a traditional TCAM of depth *D* and width *W* by cascading SRAM blocks of size  $R_D \times R_W$  on FPGAs. The minimum overall SRAM memory requirement of the existing SRAM-based TCAM solutions on FPGAs can be formulated as (6) shown below:

$$\sum_{M=1}^{\frac{D}{R_W}} \sum_{N=1}^{\frac{W}{\log_2 R_D}} (R_D \times R_W) = \left(\frac{D}{R_W}\right) \left(\frac{W}{\log_2 R_D}\right) (R_D \times R_W) = DW \left(\frac{R_D}{\log_2 R_D}\right) \quad (1)$$

The overall memory requirement of the proposed design for the implementation of a  $D \times W$  size traditional TCAM using  $R_D \times R_W$  size SRAM blocks is devised as (7) shown below:

$$\sum_{M=1}^{\frac{D}{R_W}} \sum_{N=1}^{\frac{W}{Plog_2(R_D/P)}} (R_D \times R_W)$$

$$= \left(\frac{D}{R_W}\right) \left(\frac{W}{Plog_2(R_D/P)}\right) (R_D \times R_W)$$

$$= DW \left(\frac{R_D}{Plog_2(R_D/P)}\right) \quad (2)$$

Equation (7) describes that the SRAM memory usage of our proposed design is  $\frac{R_D}{Plog_2(R_D/P)}$  times that of the corresponding traditional TCAM table of size  $D \times W$ .

Our proposed design achieves a considerable reduction in the SRAM memory usage by a factor of  $\frac{1}{P[1-log_2P/log_2R_D]}$ , when compared with that of the existing

approaches as described using (3) as follows:

$$\frac{DW\left(\frac{R_D}{Plog_2(R_D/P)}\right)}{DW\left(\frac{R_D}{log_2R_D}\right)} = \frac{log_2R_D}{Plog_2(R_D/P)}$$

$$= \frac{log_2R_D}{P[log_2R_D - log_2P]} = \frac{1}{P[1 - log_2P/log_2R_D]}$$

(3)

The usage of BRAMs in our proposed design is compared with those of previous approaches in Column 5 of Table 3. Our proposed TCAM design CASE-I emulates a 14 Kb traditional TCAM, achieving a lower BRAMs utilization of 8 BRAMs compared with the usage of 56, 40, 40, 32, and 64 BRAMs for previous approaches in [20], [21], [22], [37], and [25], respectively for an 18 Kb traditional TCAM emulation. The proposed design CASE-III emulates a large TCAM of size  $1024 \times 140$  using 80 BRAMs. It achieves a lower BRAMs utilization compared with the large TCAM implementations of size  $1024 \times 150$  and  $504 \times 180$  in the previous approaches [17] and [36], using 272 and 140 BRAMs, respectively.

#### 2. Throughput

The operational speed of our proposed design is compared with those of previous approaches in column 4 of Table 3. Our proposed design cases I and II emulates traditional TCAM of size 14 Kb and 16 Kb achieving operating frequencies of 119 MHz and 237 MHz with multipumping factors of P = 4 and 2 respectively. The operating frequency of our proposed design CASE-II is higher than previous works in [20, 21, 22, 25, 37] for an 18 Kb traditional TCAM emulation.

Our proposed design methodology is more useful for the design of large storage capacity TCAMs. The TCAM memory units of our proposed design *AND*-accumulate SRAM words from the sub-blocks of the SRAM blocks in

each system cycle, reducing the complexity of the *AND* operation units of the overall architecture, as shown in Figures 6 and 7. This further prevents the *AND* operation units from limiting the operating frequency of wide pattern TCAMs designs on FPGA. Our proposed design uses fewer BRAMs, thus alleviating the overall routing complexity of the design on FPGA. The divided *AND* operation complexity and reduced routing complexity makes our proposed design more practical for large storage capacity TCAMs.

The system frequency of our proposed design CASE-III emulating a large capacity TCAM of 140 Kb is 87 MHz, which is comparable with the maximum achievable frequency 97 MHz in previous work [17] implementing a large size TCAM of 150 Kb. While the SRAM memory usage of our proposed design CASE-III is 70% lower than that of [17].

Our proposed design provides increased design flexibility in terms of the speed vs memory usage tradeoff. The designer must consider the important design factors such as the required storage capacity, relative availability of BRAMs on the target FPGA, and required throughput for the selection of the multipumping factor in our proposed design.

#### **3.** Performance per Memory

Considering the time-space tradeoff, we used the performance evaluation metric *performance per memory* from [49], given by (8).

$$\frac{Throughput(Gb/s)}{Normalized Memory [Memory(Kb)/TCAM Depth]}$$

(4)

Table 3 compares the performance per memory of our design with previous FPGA-based TCAMs. The depth and pattern width of traditional TCAMs implemented in previous studies are listed in the third column. For a fair

comparison, the speed results of the compared works with technology differences are normalized to 40 nm, using (9) from [50]. The speed results in parenthesis represent the original data reported in the respective papers.

$$T^* = T \times \left[\frac{40(nm)}{Technology(nm)}\right] \times \left[\frac{VDD}{1.0}\right]$$

(5)

where *T* represents the original delay time, and  $T^*$  denotes the normalized delay time for 40 nm CMOS technology with a supply voltage of 1.0 V. The proposed design cases I and II implemented 14 Kb and 16 Kb traditional TCAMs using 288 Kb and 576 Kb SRAM memory with operating frequencies of 119 MHz and 237 MHz, respectively. The proposed design cases I and II achieved a performance per memory of 5.78 ((*Gb/s* × *TCAMDepth*)/*Kb*) and 6.58 ((*Gb/s* × *TCAMDepth*)/*Kb*), respectively.

| Architecture FPGA | TCAM size       | Speed             | BRAMs    | Memory  | Throughput | <b>P/M</b> <sup>(a)</sup> |      |

|-------------------|-----------------|-------------------|----------|---------|------------|---------------------------|------|

| Arcintecture      | rennecture FPGA | $(D \times W)$    | (MHz)    | (36 Kb) | usage (Kb) | (Gb/s)                    |      |

| Locke-[37]        | Virtex-6        | 512 × 36          | 166      | 64      | 2304       | 5.84                      | 1.3  |

| Jiang-[17]        | Virtex-7        | $1024 \times 150$ | 97 (139) | 272     | 9792       | 14.26                     | 1.49 |

| Qian-[36]         | Virtex-6        | $504 \times 180$  | 133      | 140     | 5040       | 23.38                     | 2.34 |

| <b>REST-[25]</b>  | Kintex-7        | $72 \times 28$    | 35 (50)  | 1       | 36         | 0.96                      | 1.92 |

| HP-TCAM-[20]      | Virtex-6        | 512 × 36          | 118      | 56      | 2016       | 4.15                      | 1.05 |

| Z-TCAM-[21]       | Virtex-6        | 512 × 36          | 159      | 40      | 1440       | 5.59                      | 1.99 |

| E-TCAM-[22]       | Virtex-6        | 512 × 36          | 164      | 40      | 1440       | 5.77                      | 2.05 |

| UE-TCAM-[16]      | Virtex-6        | 512 × 36          | 202      | 32      | 1152       | 7.1                       | 3.16 |

| Proposed CASE-I   | Virtex-6        | $512 \times 28$   | 119      | 8       | 288        | 3.25                      | 5.78 |

| Proposed CASE-II  | Virtex-6        | 512 × 32          | 237      | 16      | 576        | 7.41                      | 6.59 |

| Proposed CASE-III | Virtex-6        | $1024 \times 140$ | 87       | 80      | 2880       | 11.90                     | 4.25 |

Table 3: Performance per memory comparison of the proposed TCAM with previous approaches.

<sup>(a)</sup> **P/M**: Performance per memory  $((Gb/s \times TCAM \ Depth)/Kb)$

Table 3 shows that the performance per memory of the proposed design cases I and II are 1.83 times higher than that of UE-TCAM [16], which was the highest among the existing methods. Our proposed design CASE-III emulates a large TCAM of size  $1024 \times 140$ , achieving the performance per memory of 4.25  $((Gb/s \times TCAMDepth)/Kb))$ , which is 2.85 times higher than for large TCAM of size  $1024 \times 150$  in the existing study [17].

Our proposed design scales well in terms of the performance when evaluated for the design of a large storage capacity. Table 3 shows that the performance per memory of our proposed design CASE-III is slightly lower than the proposed design CASE-I (with the same multipumping factor of P = 4) while the implemented TCAM size of CASE-III is ten times greater than that of CASE-I.

## III. PRE-CLASSIFICATION- BASED ENERGY-EFFICIENT SRAM-BASED TCAM ARCHITECTURE

## A. Proposed Classification Scheme

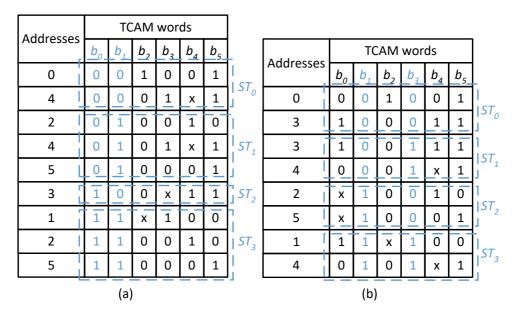

The proposed design uses the bits extracted from specific bit positions of the TCAM words to classify the TCAM table words into groups called as TCAM sub-tables. In the proposed partitioning scheme we extract  $log_2M$  classification bits from the specified bit positions of the TCAM words to produce M sub-tables. For example, suppose two bits are used for the classification of a sample TCAM table of size  $6 \times 6$  is presented in Table 4. The TCAM table presented in Table 4 is classified using two different set of bit positions  $S_1 = \{b_0, b_1\}$  and  $S_2 = \{b_1, b_3\}$ as shown in Figure 9a,b, respectively. The sub-tables constructed based on the bit values (00, 01, 10, and 11) of bit positions  $\{b_0, b_1\}$  are shown in Figure 9a. The number of TCAM words in the constructed sub-tables  $ST_0$ ,  $ST_1$ ,  $ST_2$  and  $ST_3$ varies based on the pattern of bits in the bit positions  $\{b_0, b_1\}$  selected for the classification of Table 4. TCAM words with 'x' as bit value in the classification bit positions are stored in more than one sub-table. For example, the TCAM word at address 2 has the bit values of 'x1' at  $\{b_0, b_1\}$ , and is thus stored in both subtables  $ST_1$  and  $ST_3$ . This redundancy expands the resultant TCAM sub-tables. The classification of any realistic dataset based on a specific set of bit positions may not necessarily produce sub-tables of the same size.

| Address | TCAM Words |

|---------|------------|

| 0       | 001001     |

| 1       | 11x100     |

| 2       | x10010     |

| 3       | 100x11     |

| 4       | 0x01x1     |

| 5       | x10001     |

Table 4: A TCAM table of size  $6 \times 6$ .

Figure 9: Example of the proposed classification algorithm: (a) Description of Classification based on set of bit positions  $S_1 = \{b_0, b_1\}$ . (b) Description of Classification based on set of bit positions  $S_2 = \{b_1, b_3\}$ .

The proposed solution is based on the concept that the classification effectiveness of a set of bit positions varies from that of other bit positions for

a specific dataset when the target of the classification is to construct balancedsize sub-tables. The classification example of the TCAM table in Table 4 using two different sets of bit positions is illustrated in Figure 9. It shows that the classification using  $S_2 = \{b_1, b_3\}$  is more effective for the TCAM table presented in Table 4, as the constructed sub-tables are of balanced size (2), when compared with the unbalanced size sub-tables constructed for bit positions  $S_1 = \{b_0, b_1\}$  (2, 3, 1, and 3) as explained above.